Первый слайд презентации

Основы языка VHDL Описание типовых дискретных устройств (автоматы). Подпрограммы, пакеты. Тема 6

Слайд 2: Представление автоматов

C пособы задания автоматов: таблицы переходов и выходов, граф переходов, текстовое описание. Интервалы времени между моментами допустимости изменений состояния будем называть тактами работы и нумеровать целыми числами, начиная от нуля. Состояние автомата в любом такте кроме нулевого определяется состоянием в предыдущем такте и входными сигналами. Чтобы задать конечный автомат надо определить шестерку: A ={ S, X, Y, F, V, s (0) }, где S – множество допустимых состояний; X – множество возможных входов; Y – множество выходов; F – функция переходов автомата; V – функция выходов автомата; s (0) – начальное состояние.

Слайд 3: Представление автоматов

Множества S, X, Y – конечные, S ={ s0,s1,….sp,…….sn}; X ={ x0,x1,….xr…….sm}; Y ={ yo, y 1,…. ys,……. yk }. Функция переходов F определяет состояние автомата в n - ом такте работы в зависимости от состояния автомата и входа в (n -1 )- ом такте: s(n)= F (s(n-1),x(n-1)). Для модели Мура выход целиком определяется состоянием автомата в текущий момент времени y ( n )= V ( s ( n )). Модель Мили, существует в двух модификациях с синхронизированным выходом: выход в каждом такте зависит от состояния и входа в предыдущем такте y(n) =V (s(n-1),x(n-1)) 2. с асинхронным выходом предполагает: выход определяется состоянием автомата и входом в текущем такте y(n) =V (s(n),x(n)).

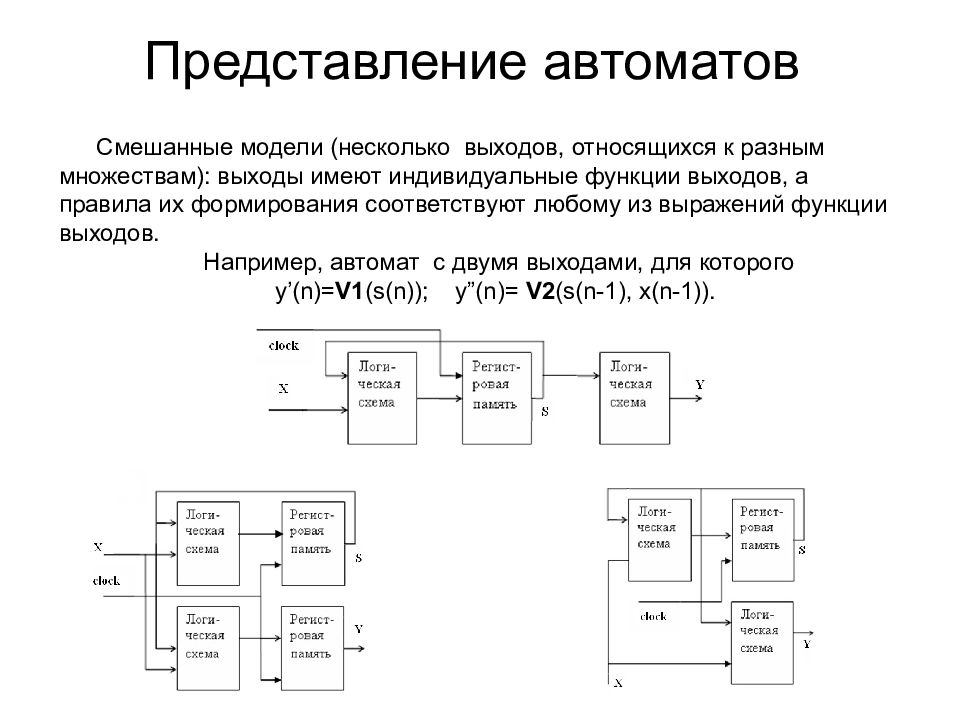

Слайд 4: Представление автоматов

C мешанные модели (несколько выходов, относящихся к разным множествам): выходы имеют индивидуальные функции выходов, а правила их формирования соответствуют любому из выражений функции выходов. Например, автомат с двумя выходами, для которого y’(n)= V1 (s(n)); y”(n)= V2 (s(n-1), x(n-1)).

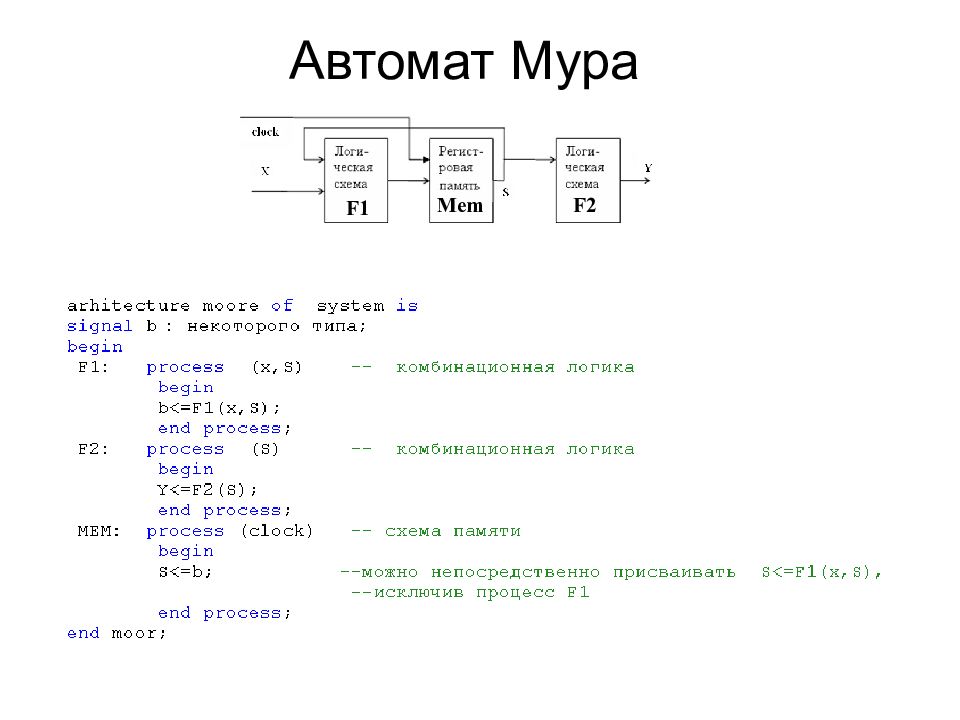

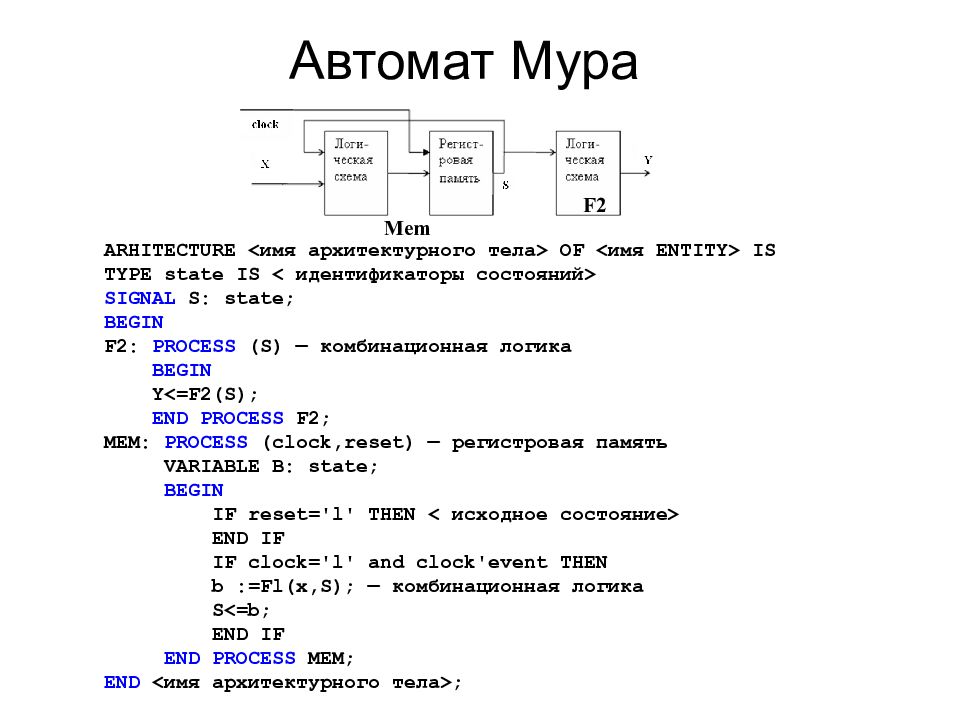

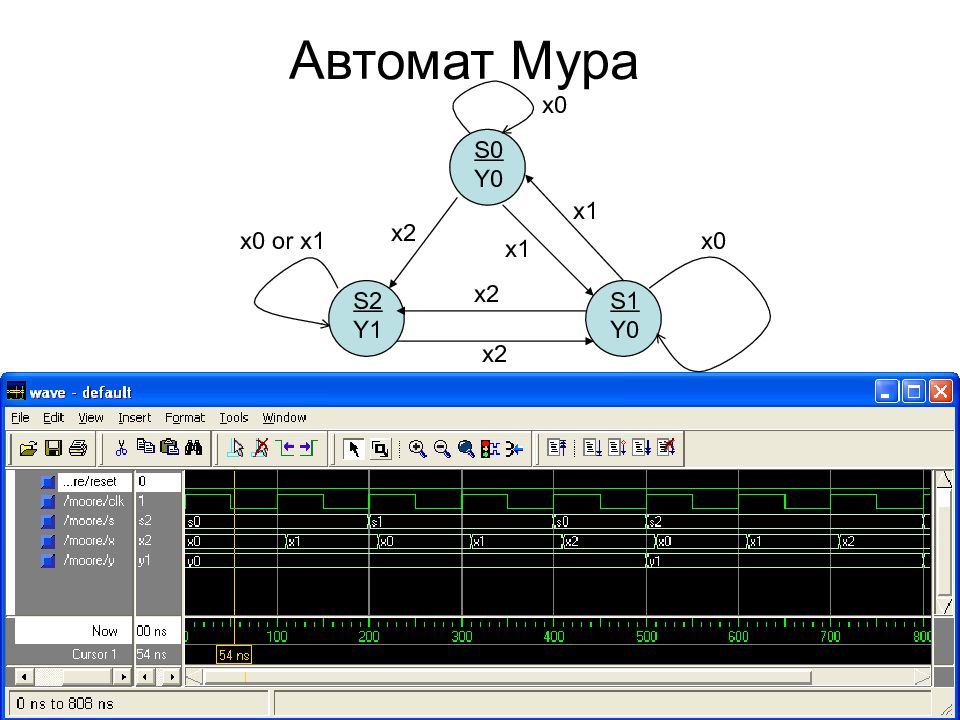

Слайд 6: Автомат Мура

A R HITECTURE <имя архитектурного тела> OF <имя ENTITY> IS TYPE state IS < идентификаторы состояний> SIGNAL S: state; BEGIN F2: PROCESS (S) — комбинационная логика BEGIN Y<=F2(S); END PROCESS F2; MEM: PROCESS (clock,reset) — регистровая память VARIABLE В: state; BEGIN IF reset='l' THEN < исходное состояние> END IF IF clock='l' and clock'event THEN b :=Fl(x,S); — комбинационная логика S<=b; END IF END PROCESS MEM; END <имя архитектурного тела>; F2 Mem

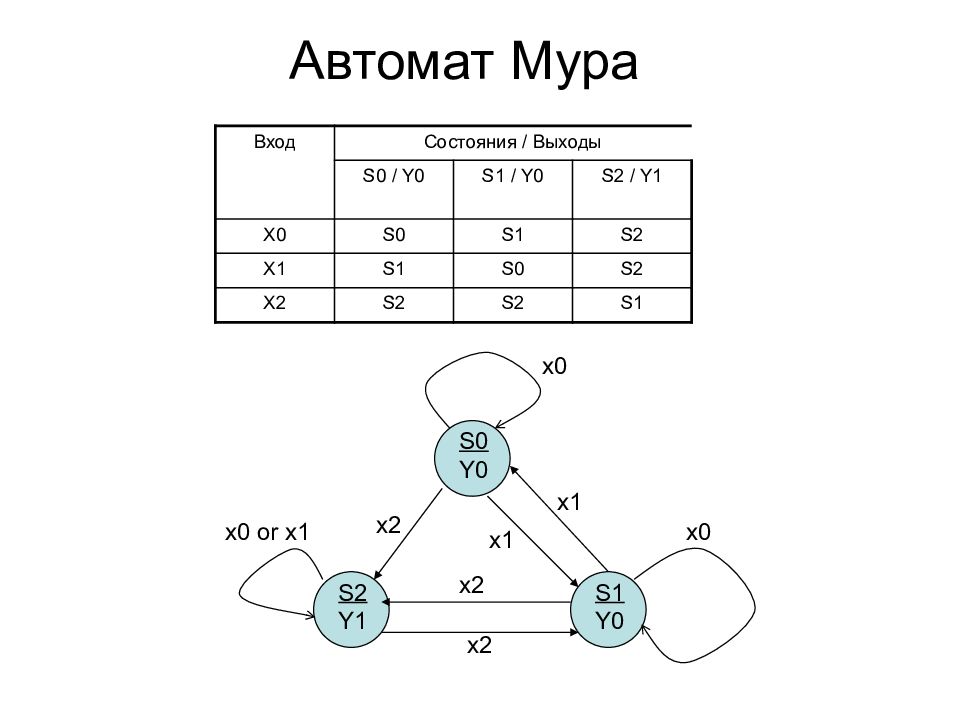

Слайд 7: Автомат Мура

Вход Состояния / Выходы S0 / Y0 S1 / Y0 S2 / Y1 X0 S0 S1 S2 X1 S1 S0 S2 X2 S2 S2 S1 S0 Y0 S2 Y1 S1 Y0 x1 x0 x0 x0 or x1 x1 x2 x2 x2

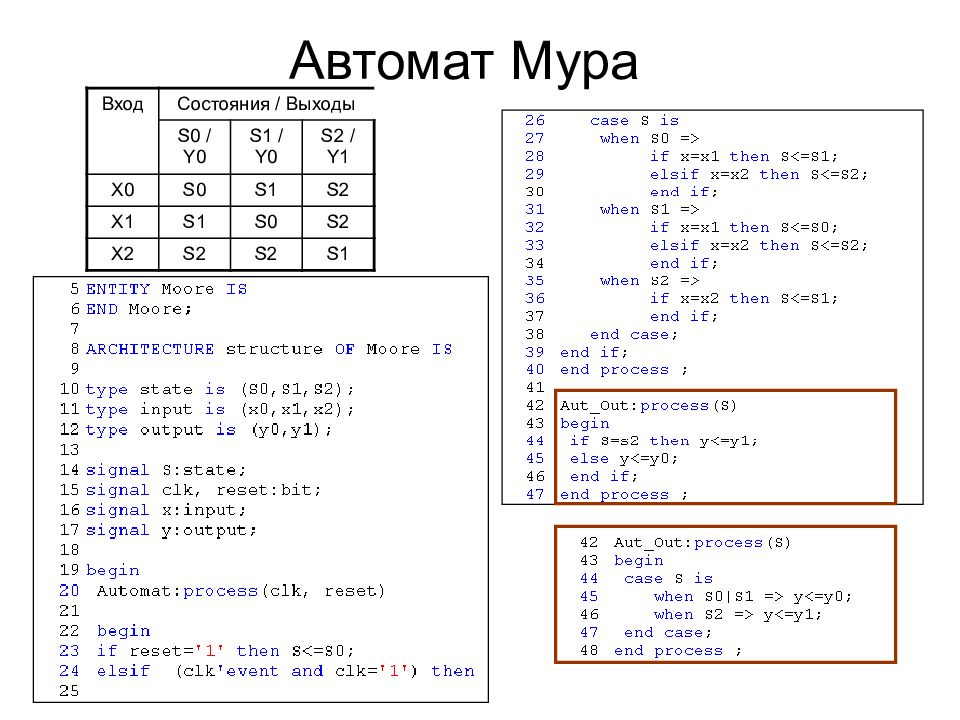

Слайд 8: Автомат Мура

Вход Состояния / Выходы S0 / Y0 S1 / Y0 S2 / Y1 X0 S0 S1 S2 X1 S1 S0 S2 X2 S2 S2 S1

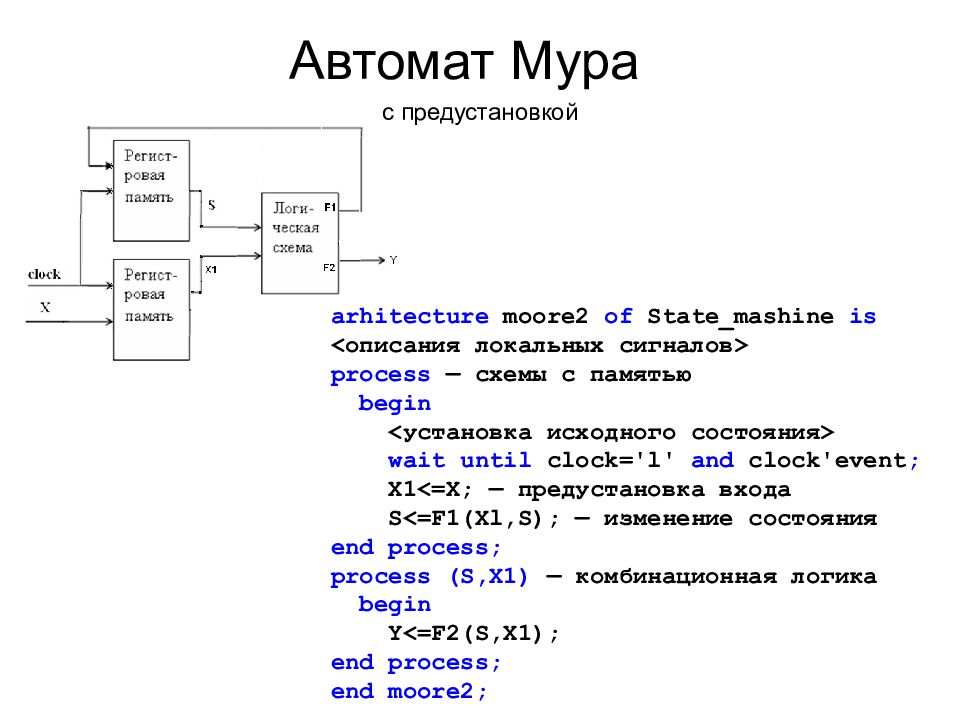

Слайд 10: Автомат Мура

с предустановкой arhitecture moore2 of State_mashine is <описания локальных сигналов> process — схемы с памятью begin <установка исходного состояния> wait until clock='l' and clock'event ; X1<=X; — предустановка входа S<=F1(Xl,S); — изменение состояния end process; process (S,X1) — комбинационная логика begin Y<=F2(S,X1); end process; end moore2;

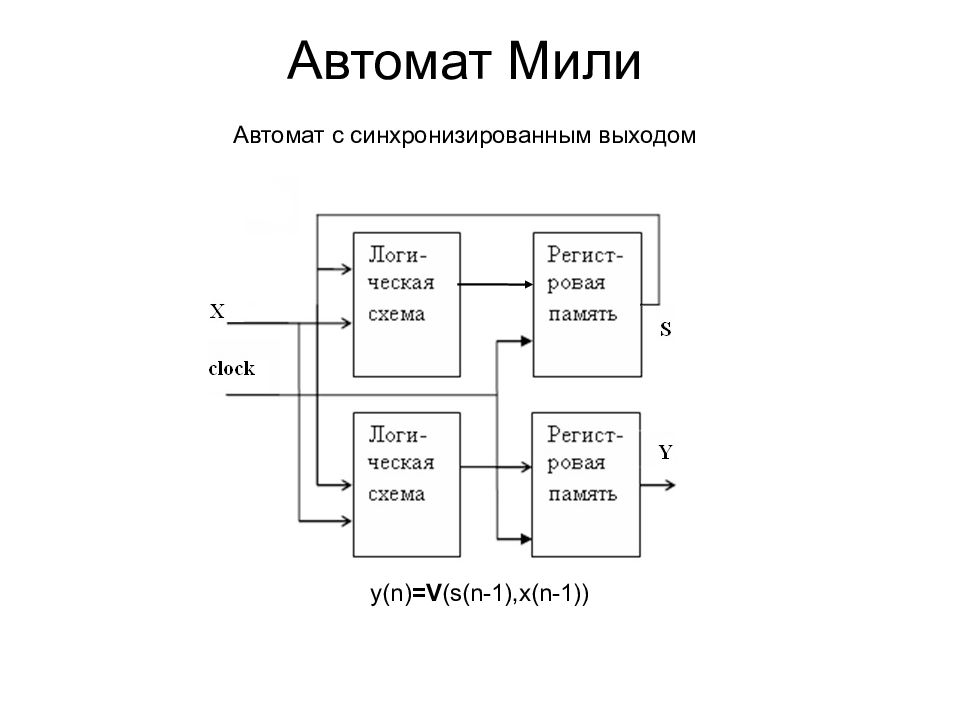

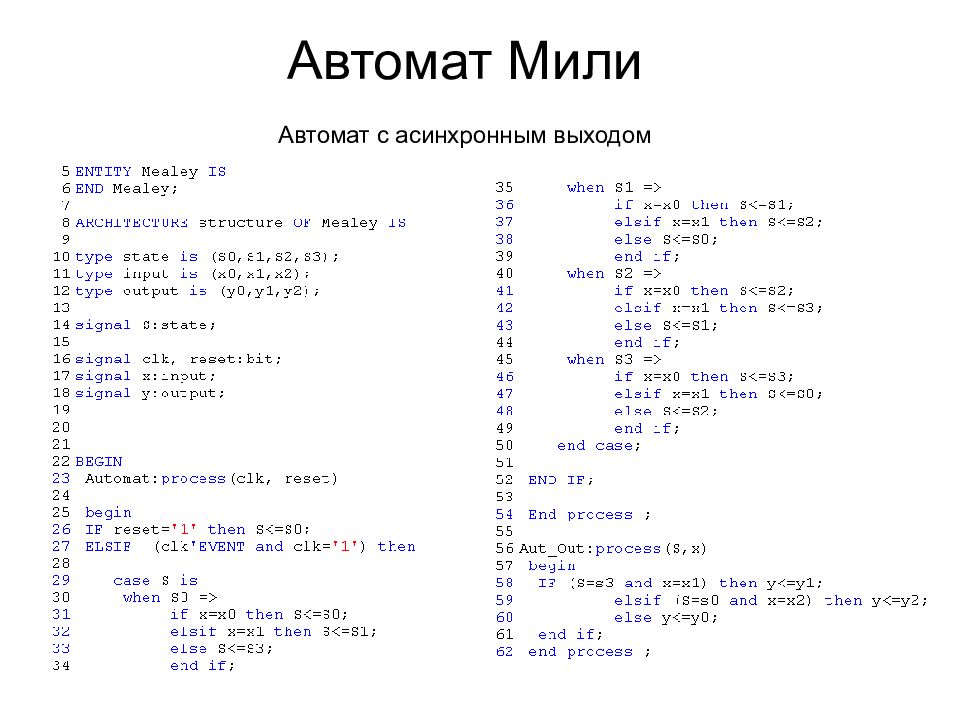

Слайд 11: Автомат Мили

Автомат с синхронизированным выходом y(n) =V (s(n-1),x(n-1))

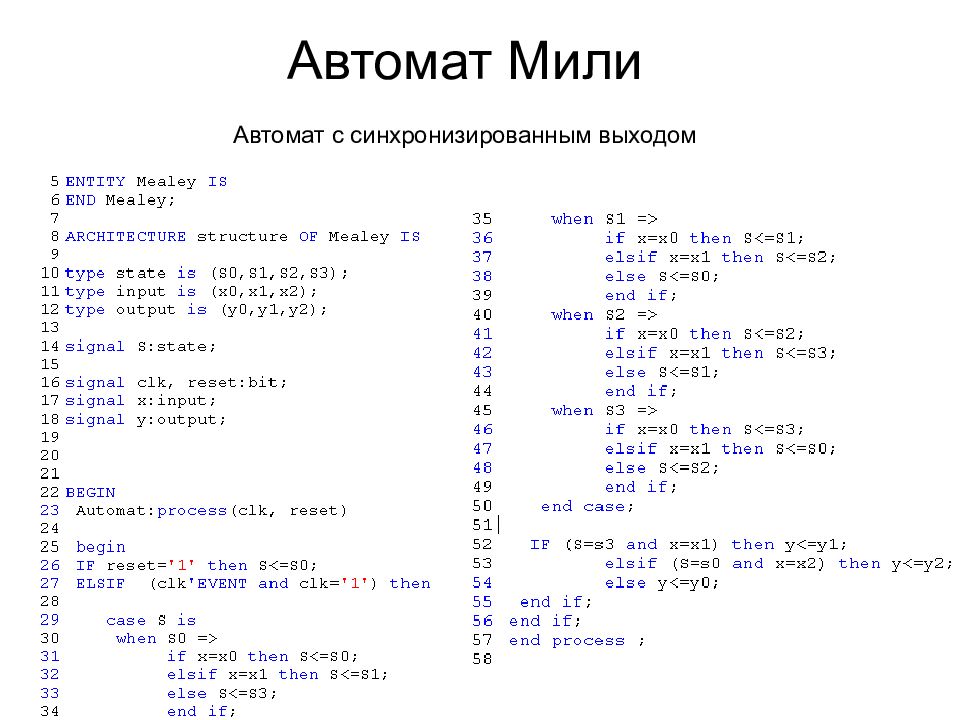

Слайд 13: Автомат Мили

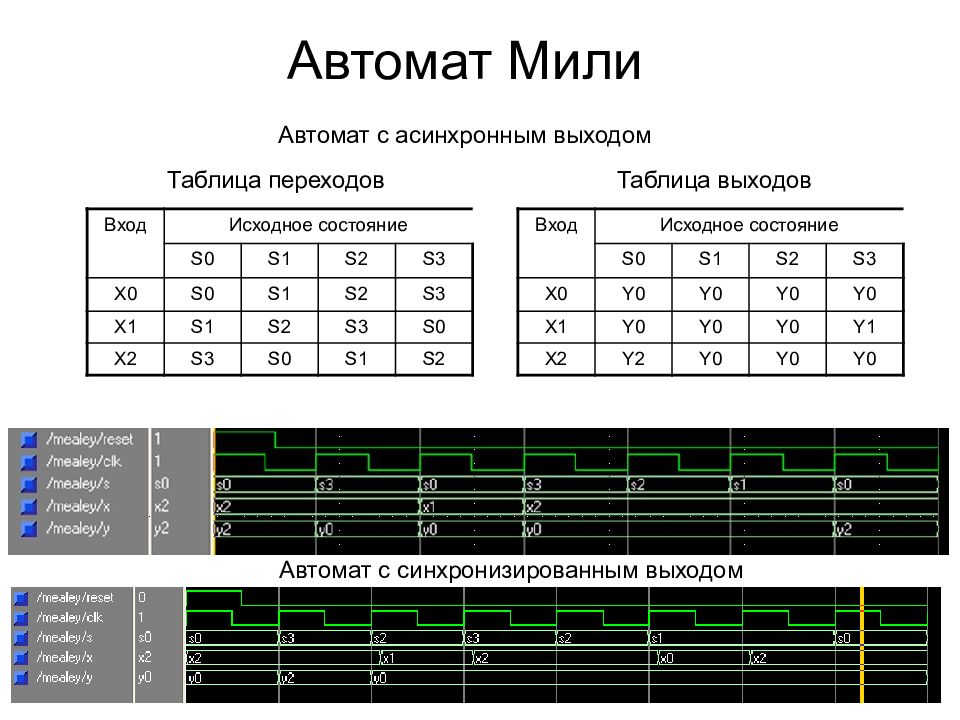

Автомат с синхронизированным выходом Вход Исходное состояние S0 S1 S2 S 3 X0 S0 S 1 S 2 S 3 X1 S1 S 2 S 3 S 0 X2 S 3 S 0 S 1 S 2 Вход Исходное состояние S0 S1 S2 S 3 X0 Y0 Y0 Y0 Y0 X1 Y0 Y0 Y0 Y1 X2 Y2 Y0 Y0 Y0 Таблица переходов Таблица выходов

Слайд 16: Автомат Мили

Автомат с асинхронным выходом Вход Исходное состояние S0 S1 S2 S 3 X0 S0 S 1 S 2 S 3 X1 S1 S 2 S 3 S 0 X2 S 3 S 0 S 1 S 2 Вход Исходное состояние S0 S1 S2 S 3 X0 Y0 Y0 Y0 Y0 X1 Y0 Y0 Y0 Y1 X2 Y2 Y0 Y0 Y0 Таблица переходов Таблица выходов Автомат с синхронизированным выходом

Слайд 17: Представление состояний автомата

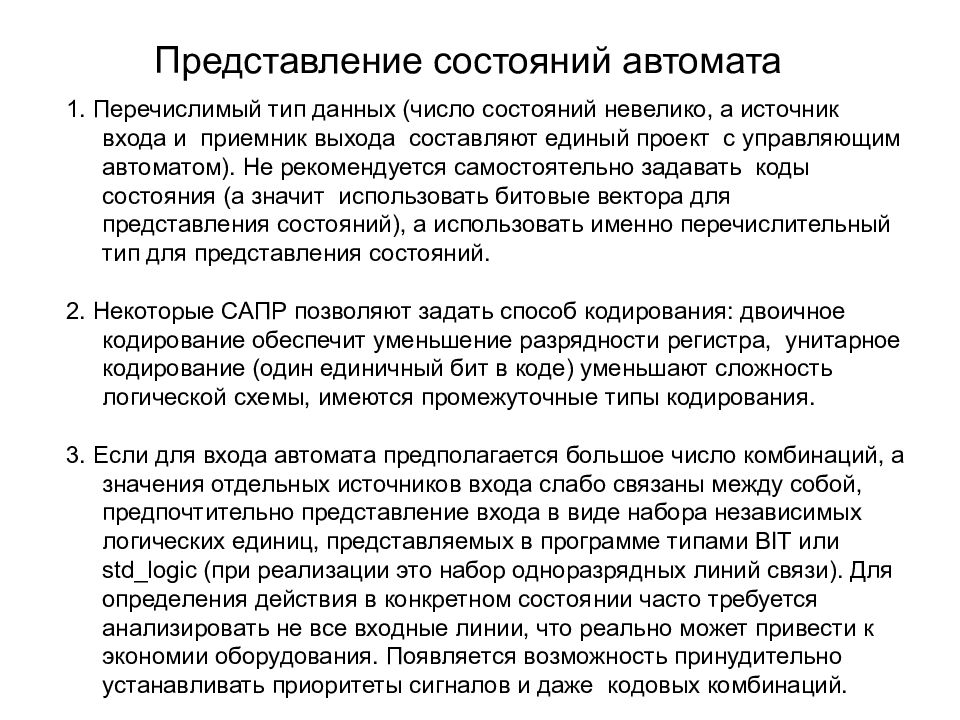

1. Перечислимый тип данных (число состояний невелико, а источник входа и приемник выхода составляют единый проект с управляющим автоматом). Не рекомендуется самостоятельно задавать коды состояния (а значит использовать битовые вектора для представления состояний), а использовать именно перечислительный тип для представления состояний. 2. Некоторые САПР позволяют задать способ кодирования: двоичное кодирование обеспечит уменьшение разрядности регистра, унитарное кодирование (один единичный бит в коде) уменьшают сложность логической схемы, имеются промежуточные типы кодирования. 3. Если для входа автомата предполагается большое число комбинаций, а значения отдельных источников входа слабо связаны между собой, предпочтительно представление входа в виде набора независимых логических единиц, представляемых в программе типами BIT или std _ logic (при реализации это набор одноразрядных линий связи). Для определения действия в конкретном состоянии часто требуется анализировать не все входные линии, что реально может привести к экономии оборудования. Появляется возможность принудительно устанавливать приоритеты сигналов и даже кодовых комбинаций.

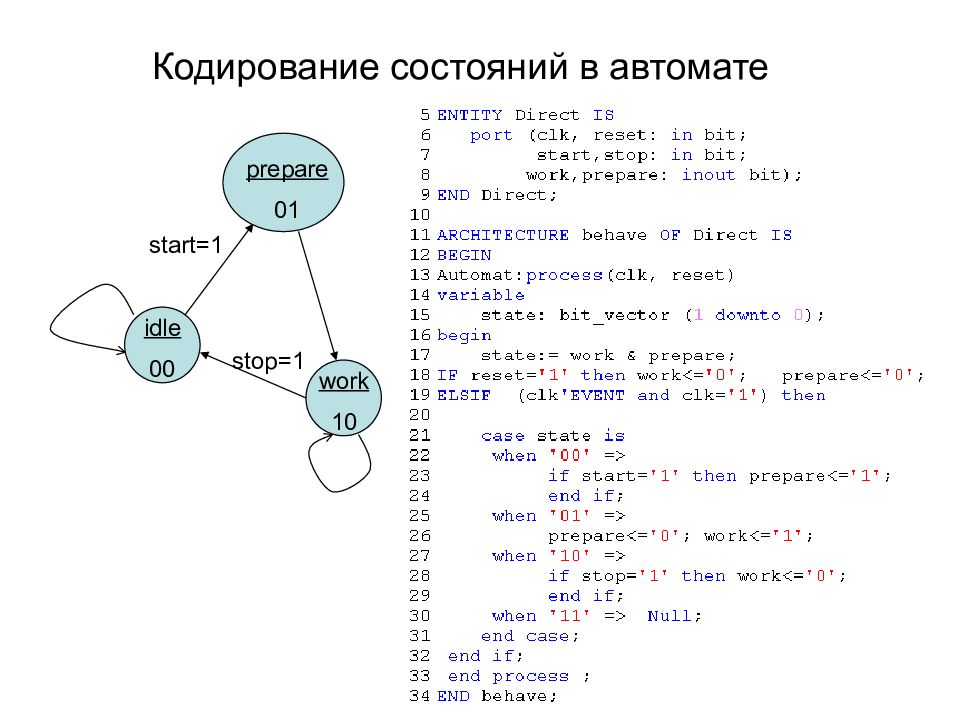

Слайд 18: Кодирование состояний в автомате

prepare 01 idle 00 stop=1 work 10 start=1

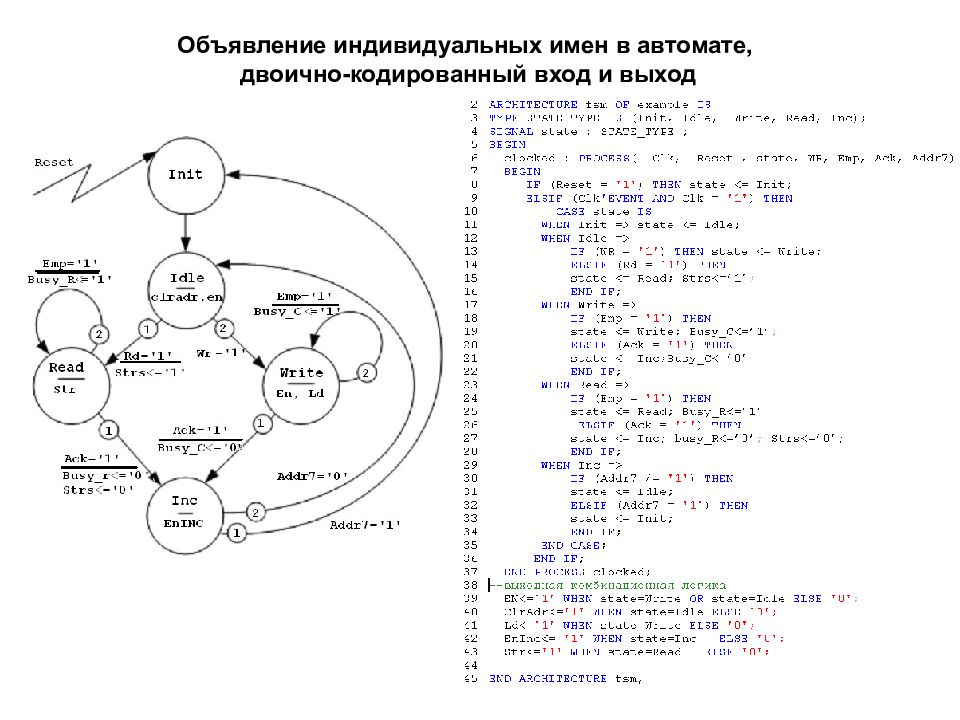

Слайд 19: Объявление индивидуальных имен в автомате, двоично-кодированный вход и выход

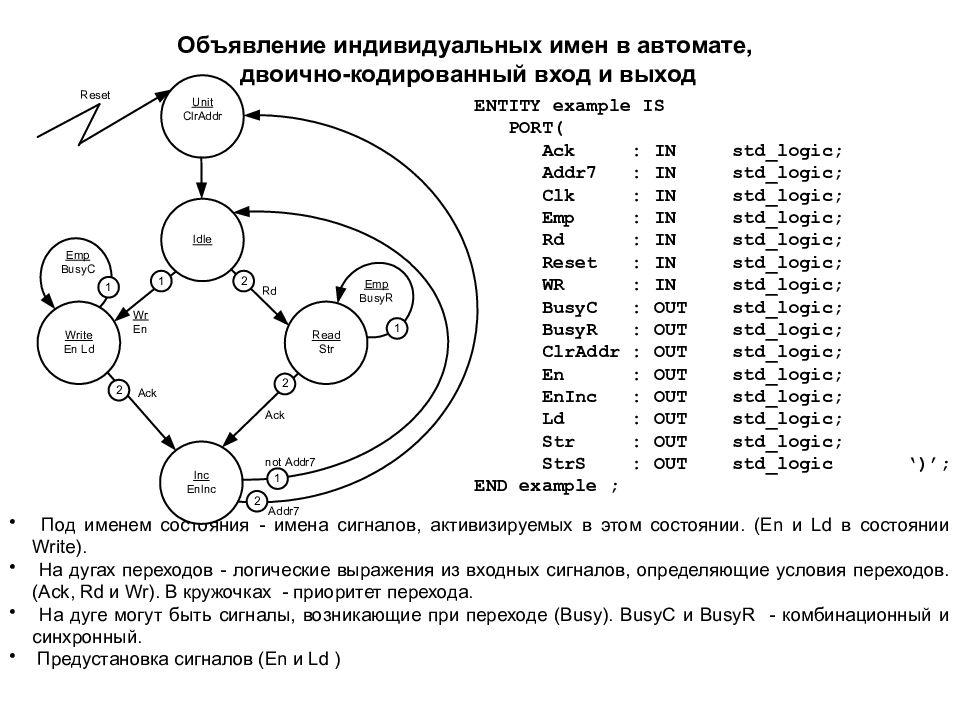

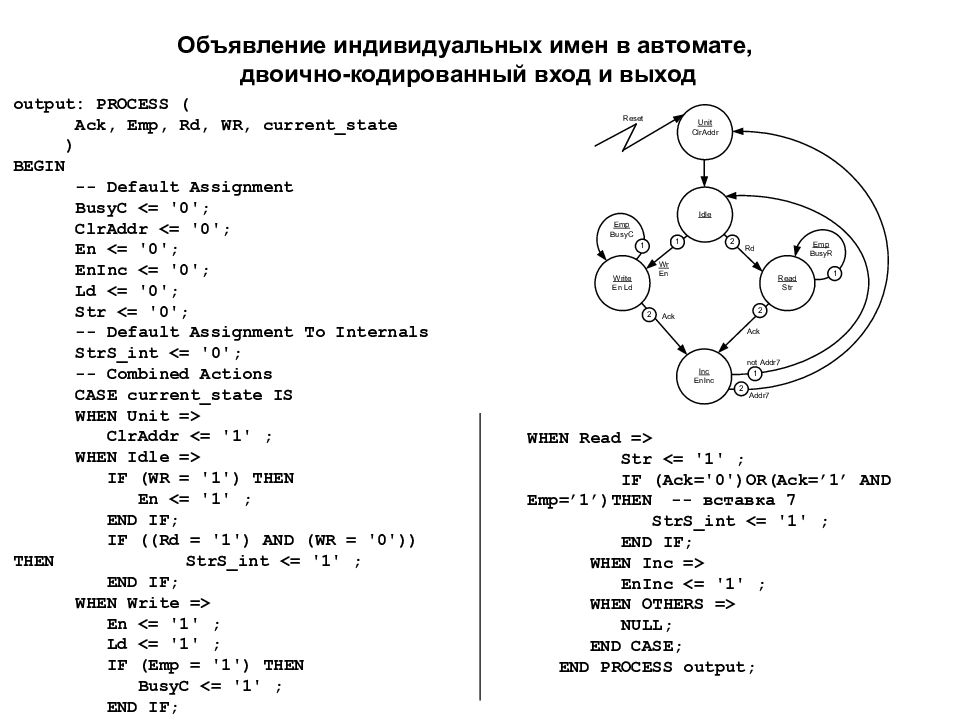

Слайд 20: Объявление индивидуальных имен в автомате, двоично-кодированный вход и выход

Под именем состояния - имена сигналов, активизируемых в этом состоянии. (En и Ld в состоянии Write). На дугах переходов - логические выражения из входных сигналов, определяющие условия переходов. (Ack, Rd и Wr). В кружочках - приоритет перехода. На дуге могут быть сигналы, возникающие при переходе (Busy). BusyC и BusyR - комбинационный и синхронный. Предустановка сигналов (En и Ld ) ENTITY example IS PORT( Ack : IN std_logic; Addr7 : IN std_logic; Clk : IN std_logic; Emp : IN std_logic; Rd : IN std_logic; Reset : IN std_logic; WR : IN std_logic; BusyC : OUT std_logic; BusyR : OUT std_logic; ClrAddr : OUT std_logic; En : OUT std_logic; EnInc : OUT std_logic; Ld : OUT std_logic; Str : OUT std_logic; StrS : OUT std_logic ‘)’; END example ;

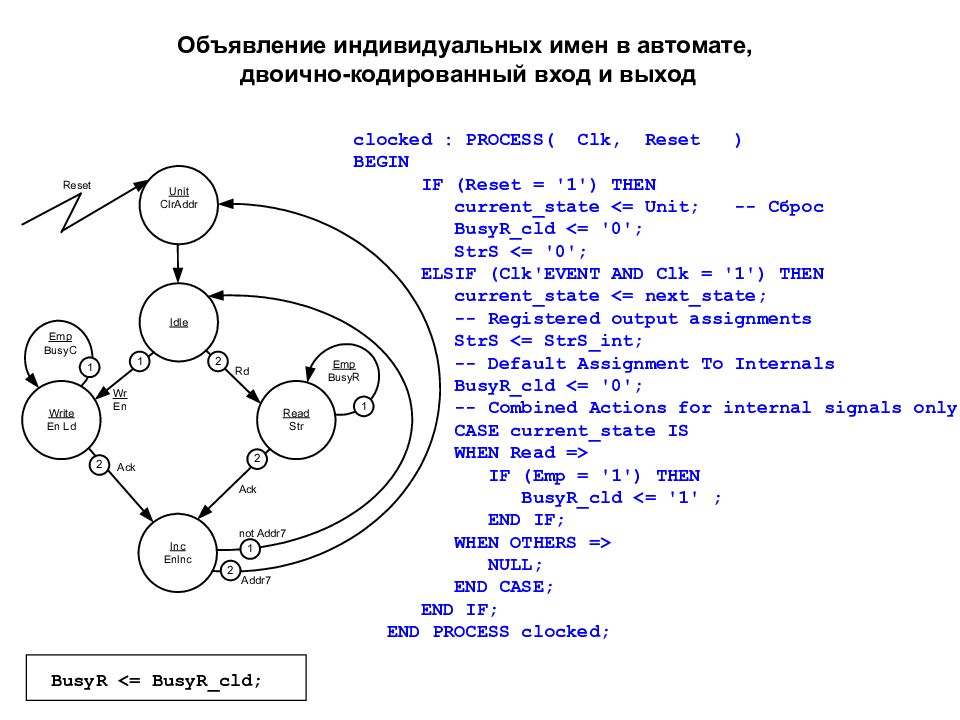

Слайд 21: Объявление индивидуальных имен в автомате, двоично-кодированный вход и выход

clocked : PROCESS( Clk, Reset ) BEGIN IF (Reset = '1') THEN current_state <= Unit; -- Сброс BusyR_cld <= '0'; StrS <= '0'; ELSIF (Clk'EVENT AND Clk = '1') THEN current_state <= next_state; -- Registered output assignments StrS <= StrS_int; -- Default Assignment To Internals BusyR_cld <= '0'; -- Combined Actions for internal signals only CASE current_state IS WHEN Read => IF (Emp = '1') THEN BusyR_cld <= '1' ; END IF; WHEN OTHERS => NULL; END CASE; END IF; END PROCESS clocked; BusyR <= BusyR_cld;

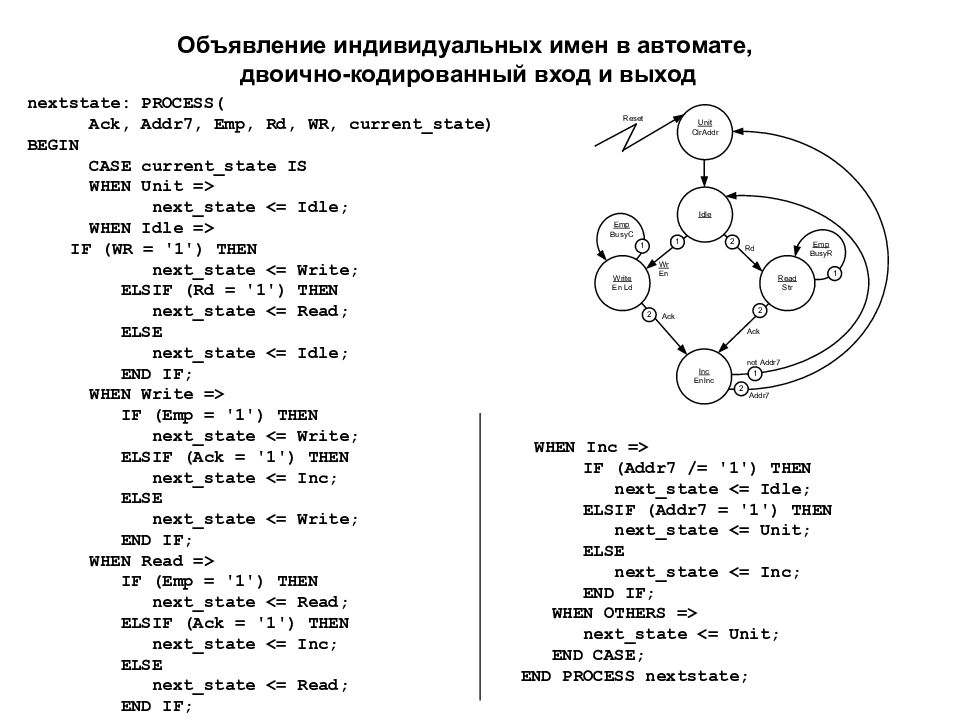

Слайд 22: Объявление индивидуальных имен в автомате, двоично-кодированный вход и выход

nextstate: PROCESS( Ack, Addr7, Emp, Rd, WR, current_state) BEGIN CASE current_state IS WHEN Unit => next_state <= Idle; WHEN Idle => IF (WR = '1') THEN next_state <= Write; ELSIF (Rd = '1') THEN next_state <= Read; ELSE next_state <= Idle; END IF; WHEN Write => IF (Emp = '1') THEN next_state <= Write; ELSIF (Ack = '1') THEN next_state <= Inc; ELSE next_state <= Write; END IF; WHEN Read => IF (Emp = '1') THEN next_state <= Read; ELSIF (Ack = '1') THEN next_state <= Inc; ELSE next_state <= Read; END IF; WHEN Inc => IF (Addr7 /= '1') THEN next_state <= Idle; ELSIF (Addr7 = '1') THEN next_state <= Unit; ELSE next_state <= Inc; END IF; WHEN OTHERS => next_state <= Unit; END CASE; END PROCESS nextstate;

Слайд 23: Объявление индивидуальных имен в автомате, двоично-кодированный вход и выход

output: PROCESS ( Ack, Emp, Rd, WR, current_state ) BEGIN -- Default Assignment BusyC <= '0'; ClrAddr <= '0'; En <= '0'; EnInc <= '0'; Ld <= '0'; Str <= '0'; -- Default Assignment To Internals StrS _ int <= '0'; -- Combined Actions CASE current_state IS WHEN Unit => ClrAddr <= '1' ; WHEN Idle => IF (WR = '1') THEN En <= '1' ; END IF; IF ((Rd = '1') AND (WR = '0')) THEN StrS_int <= '1' ; END IF; WHEN Write => En <= '1' ; Ld <= '1' ; IF (Emp = '1') THEN BusyC <= '1' ; END IF; WHEN Read => Str <= '1' ; IF (Ack='0')OR(Ack=’1’ AND Emp=’1’)THEN -- вставка 7 StrS_int <= '1' ; END IF; WHEN Inc => EnInc <= '1' ; WHEN OTHERS => NULL; END CASE; END PROCESS output;

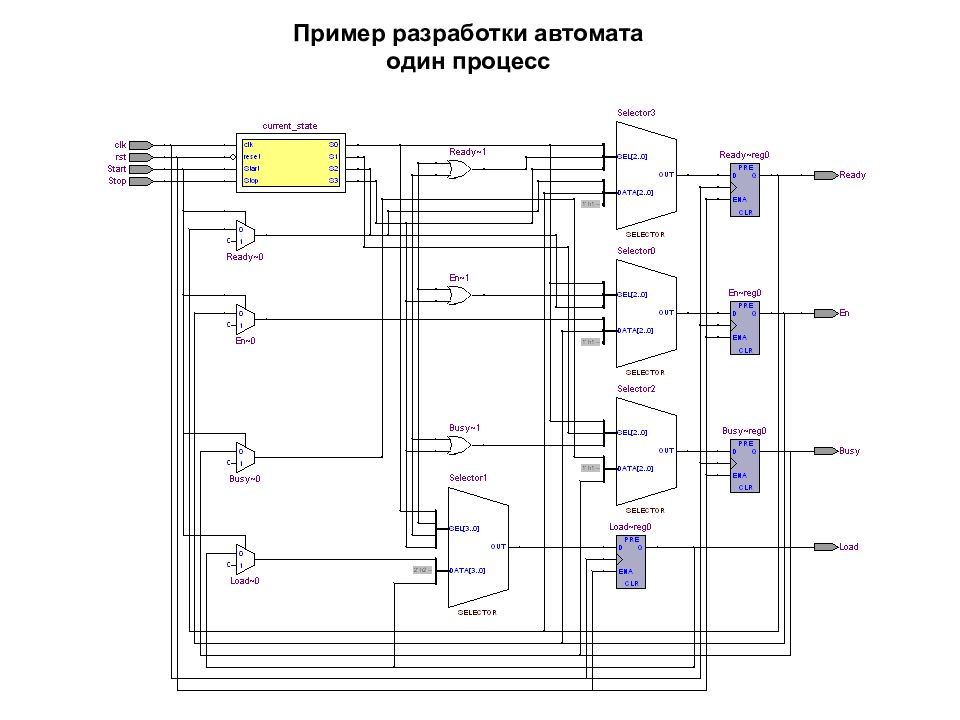

Слайд 24

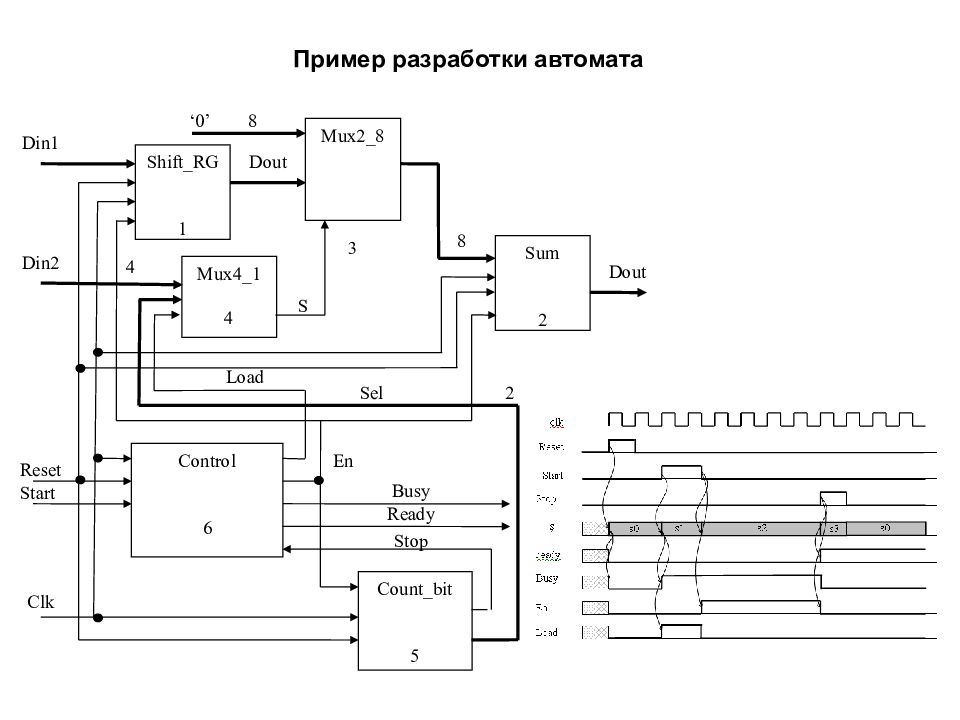

Shift_RG 1 Din1 Mux 2_8 3 Sum 2 2 8 8 Mux 4_1 4 Din 2 4 S Count _ bit 5 Clk Control 6 Reset Start Busy Ready Stop Dout En Dout ‘0’ Sel Load Пример разработки автомата

Слайд 25

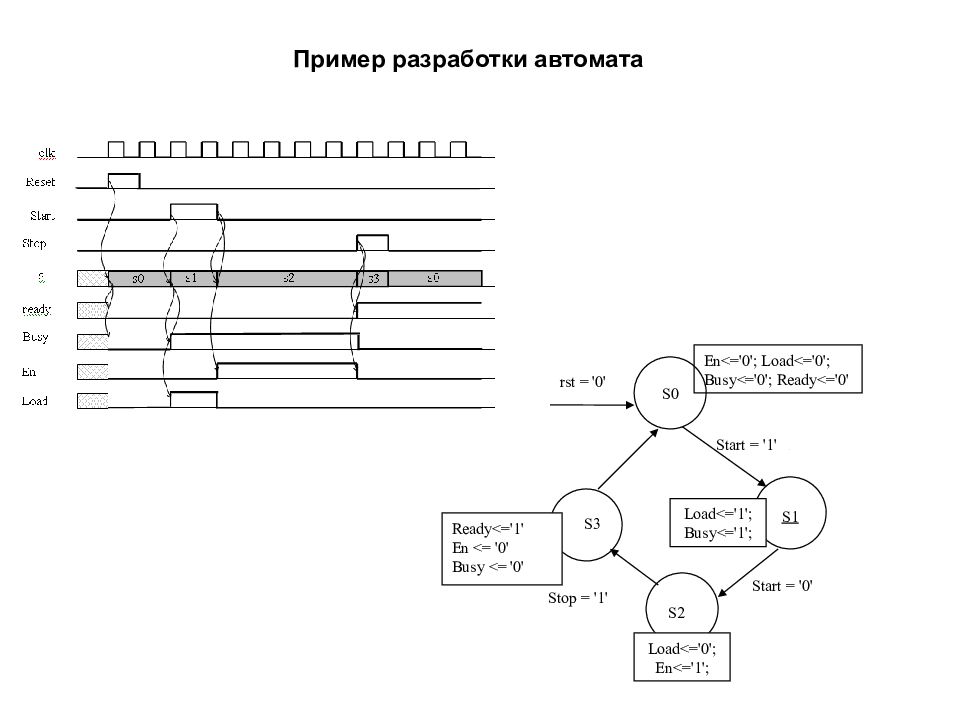

Пример разработки автомата S0 S 1 S2 S3 Start = '1', rst = '0' Load<=' 1 '; Busy<=' 1 '; Start = '0' Load<=' 0 '; En<=' 1 '; Stop = '1' Ready<='1' En <= '0' Busy <= '0' En<='0'; Load<='0'; Busy<='0'; Ready<='0'

Слайд 26

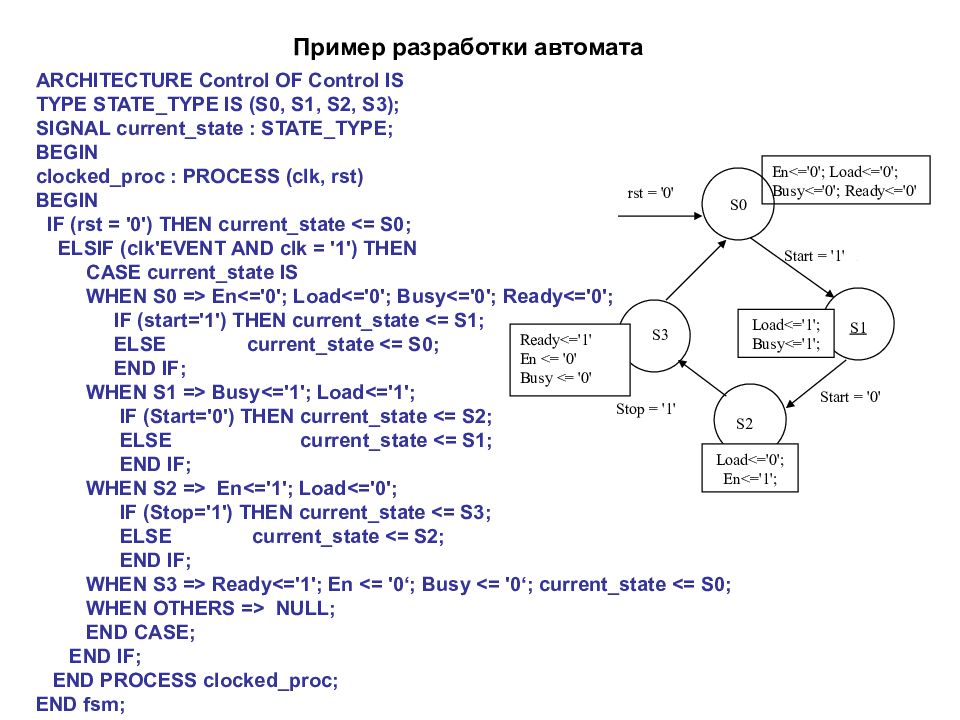

Пример разработки автомата ARCHITECTURE Control OF Control IS TYPE STATE_TYPE IS (S0, S1, S2, S3); SIGNAL current_state : STATE_TYPE; BEGIN clocked_proc : PROCESS (clk, rst) BEGIN IF (rst = '0') THEN current_state <= S0; ELSIF (clk'EVENT AND clk = '1') THEN CASE current_state IS WHEN S0 => En<='0'; Load<='0'; Busy<='0'; Ready<='0'; IF (start='1') THEN current_state <= S1; ELSE current_state <= S0; END IF; WHEN S1 => Busy<='1'; Load<='1'; IF (Start='0') THEN current_state <= S2; ELSE current_state <= S1; END IF; WHEN S2 => En<='1'; Load<='0'; IF (Stop='1') THEN current_state <= S3; ELSE current_state <= S2; END IF; WHEN S3 => Ready<='1'; En <= '0‘; Busy <= '0‘; current_state <= S0; WHEN OTHERS => NULL; END CASE; END IF; END PROCESS clocked_proc; END fsm; S0 S 1 S2 S3 Start = '1', rst = '0' Load<=' 1 '; Busy<=' 1 '; Start = '0' Load<=' 0 '; En<=' 1 '; Stop = '1' Ready<='1' En <= '0' Busy <= '0' En<='0'; Load<='0'; Busy<='0'; Ready<='0'

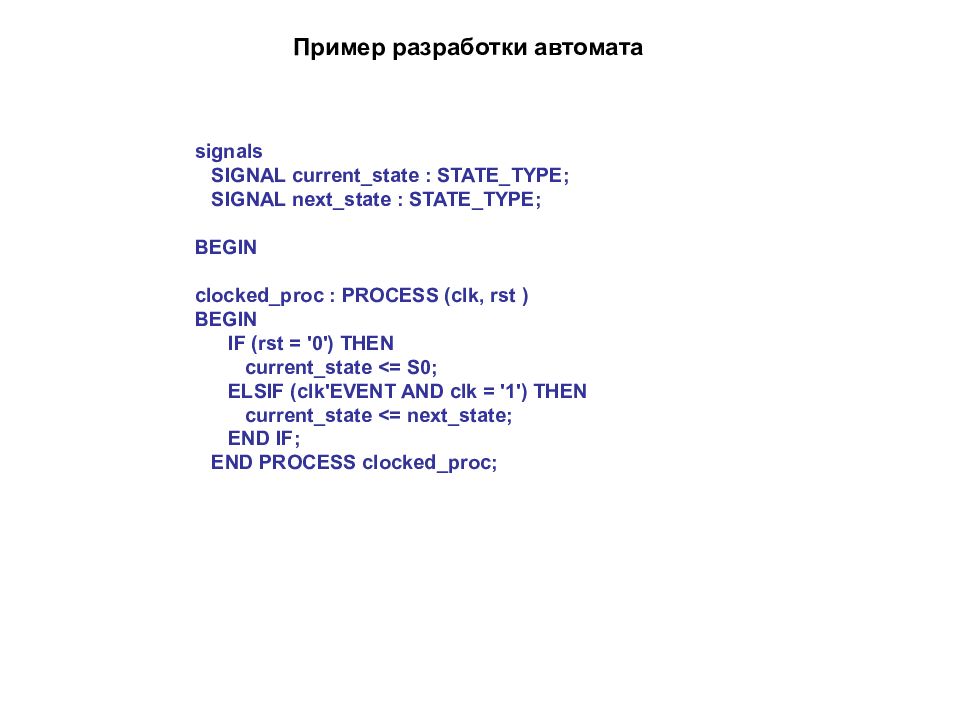

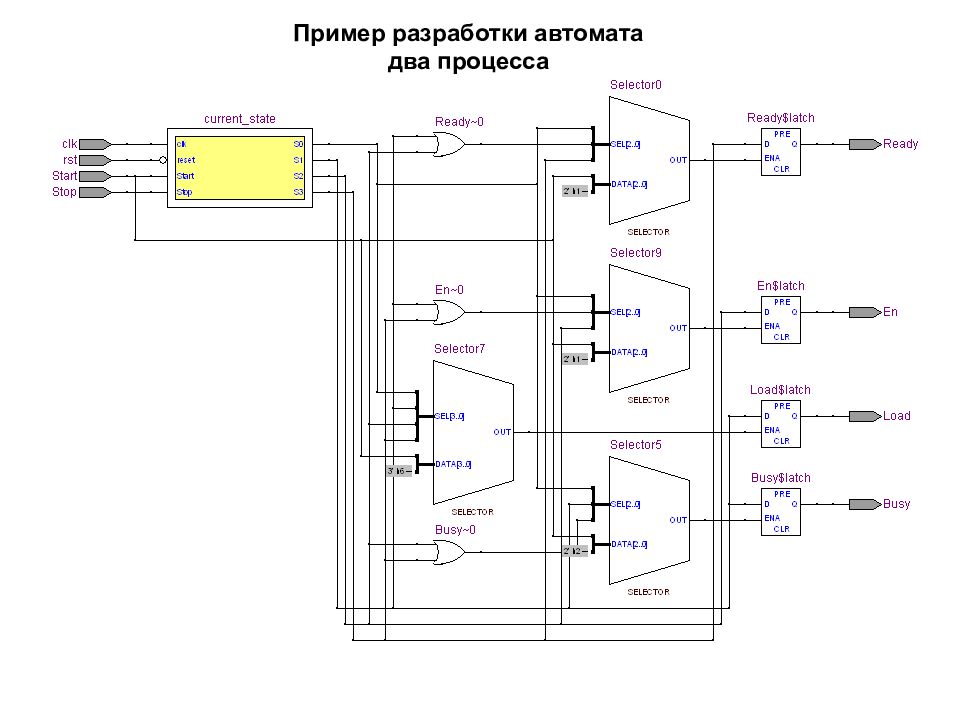

Слайд 27

Пример разработки автомата signals SIGNAL current_state : STATE_TYPE; SIGNAL next_state : STATE_TYPE; BEGIN clocked_proc : PROCESS (clk, rst ) BEGIN IF (rst = '0') THEN current_state <= S0; ELSIF (clk'EVENT AND clk = '1') THEN current_state <= next_state; END IF; END PROCESS clocked_proc;

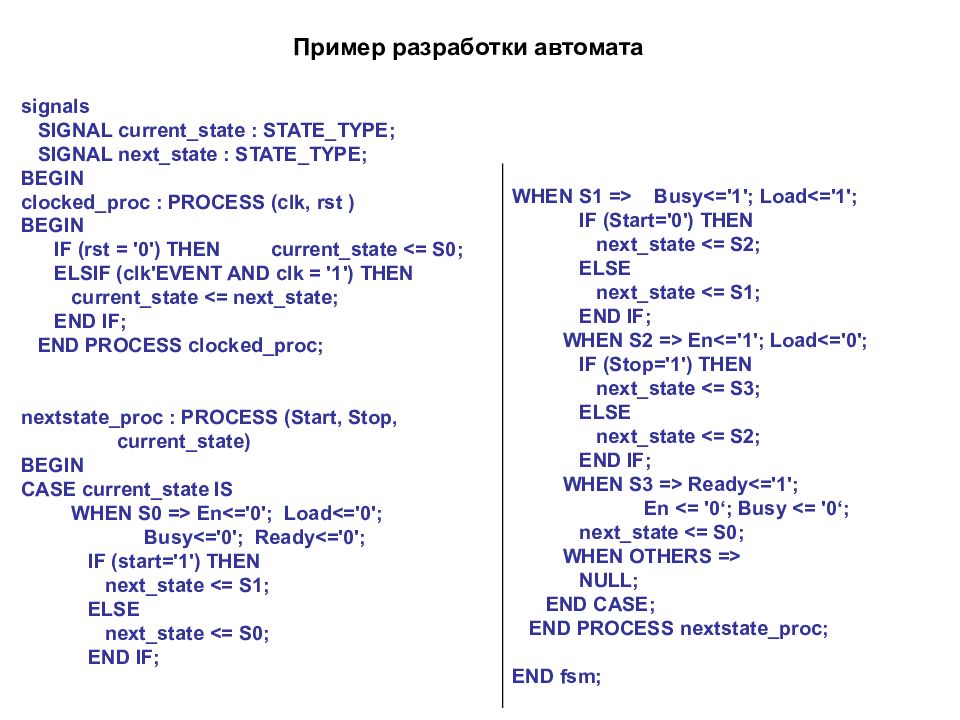

Слайд 28

Пример разработки автомата signals SIGNAL current_state : STATE_TYPE; SIGNAL next_state : STATE_TYPE; BEGIN clocked_proc : PROCESS (clk, rst ) BEGIN IF (rst = '0') THEN current_state <= S0; ELSIF (clk'EVENT AND clk = '1') THEN current_state <= next_state; END IF; END PROCESS clocked_proc; nextstate_proc : PROCESS (Start, Stop, current_state) BEGIN CASE current_state IS WHEN S0 => En<='0'; Load<='0'; Busy<='0'; Ready<='0'; IF (start='1') THEN next_state <= S1; ELSE next_state <= S0; END IF; WHEN S1 => Busy<='1'; Load<='1'; IF (Start='0') THEN next_state <= S2; ELSE next_state <= S1; END IF; WHEN S2 => En<='1'; Load<='0'; IF (Stop='1') THEN next_state <= S3; ELSE next_state <= S2; END IF; WHEN S3 => Ready<='1'; En <= '0‘; Busy <= '0‘; next_state <= S0; WHEN OTHERS => NULL; END CASE; END PROCESS nextstate_proc; END fsm;

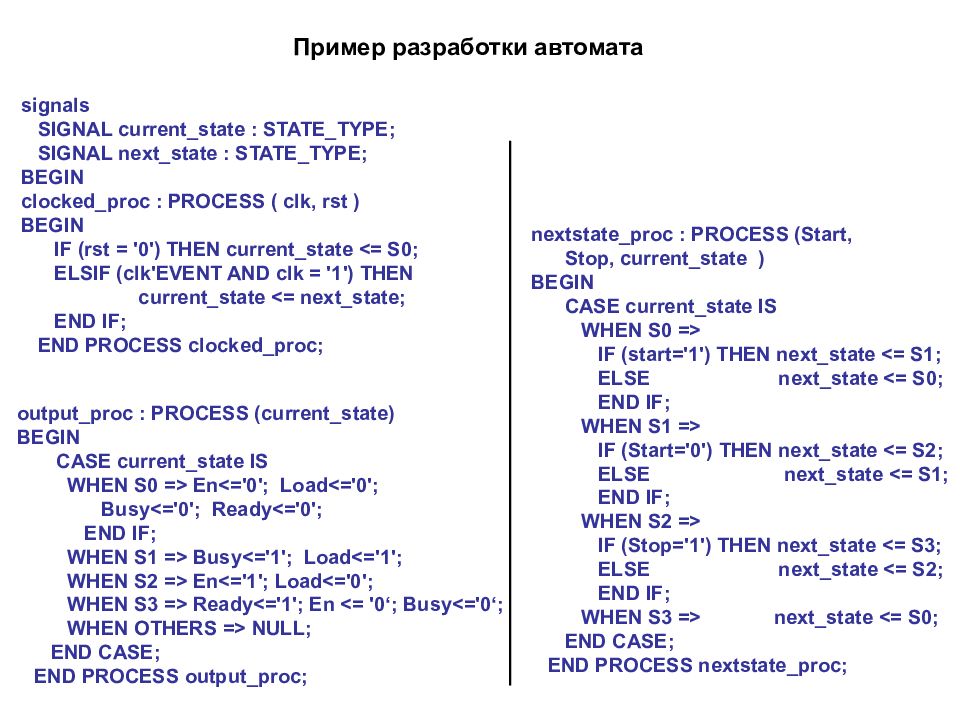

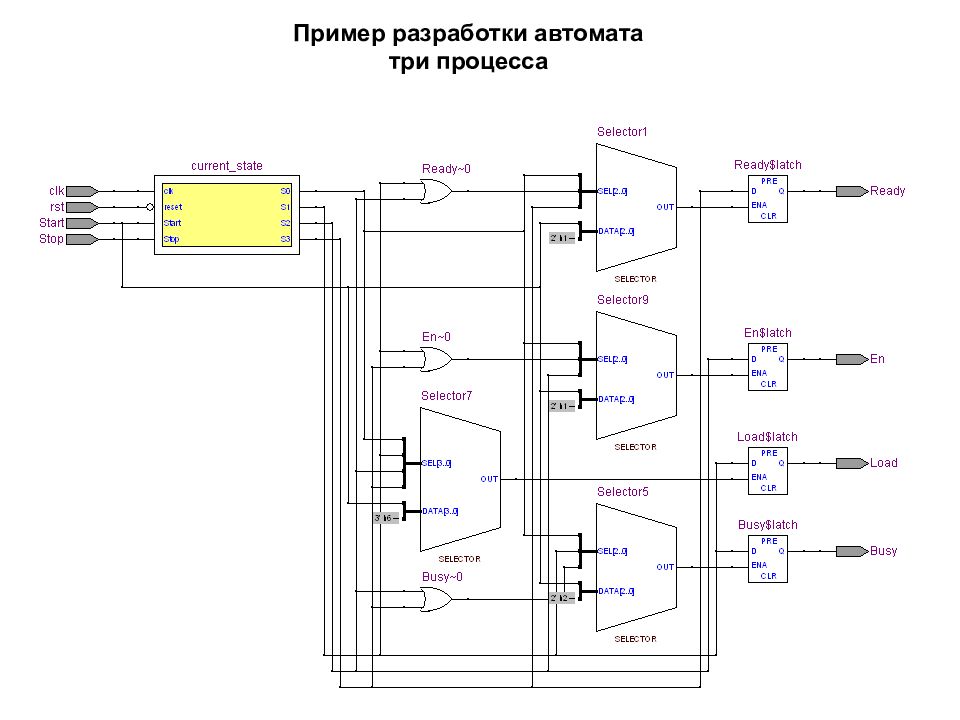

Слайд 29

Пример разработки автомата signals SIGNAL current_state : STATE_TYPE; SIGNAL next_state : STATE_TYPE; BEGIN clocked_proc : PROCESS ( clk, rst ) BEGIN IF (rst = '0') THEN current_state <= S0; ELSIF (clk'EVENT AND clk = '1') THEN current_state <= next_state; END IF; END PROCESS clocked_proc; nextstate_proc : PROCESS (Start, Stop, current_state ) BEGIN CASE current_state IS WHEN S0 => IF (start='1') THEN next_state <= S1; ELSE next_state <= S0; END IF; WHEN S1 => IF (Start='0') THEN next_state <= S2; ELSE next_state <= S1; END IF; WHEN S2 => IF (Stop='1') THEN next_state <= S3; ELSE next_state <= S2; END IF; WHEN S3 => next_state <= S0; END CASE; END PROCESS nextstate_proc; output_proc : PROCESS (current_state) BEGIN CASE current_state IS WHEN S0 => En<='0'; Load<='0'; Busy<='0'; Ready<='0'; END IF; WHEN S1 => Busy<='1'; Load<='1'; WHEN S2 => En<='1'; Load<='0'; WHEN S3 => Ready<='1'; En <= '0‘; Busy<='0‘; WHEN OTHERS => NULL; END CASE; END PROCESS output_proc;

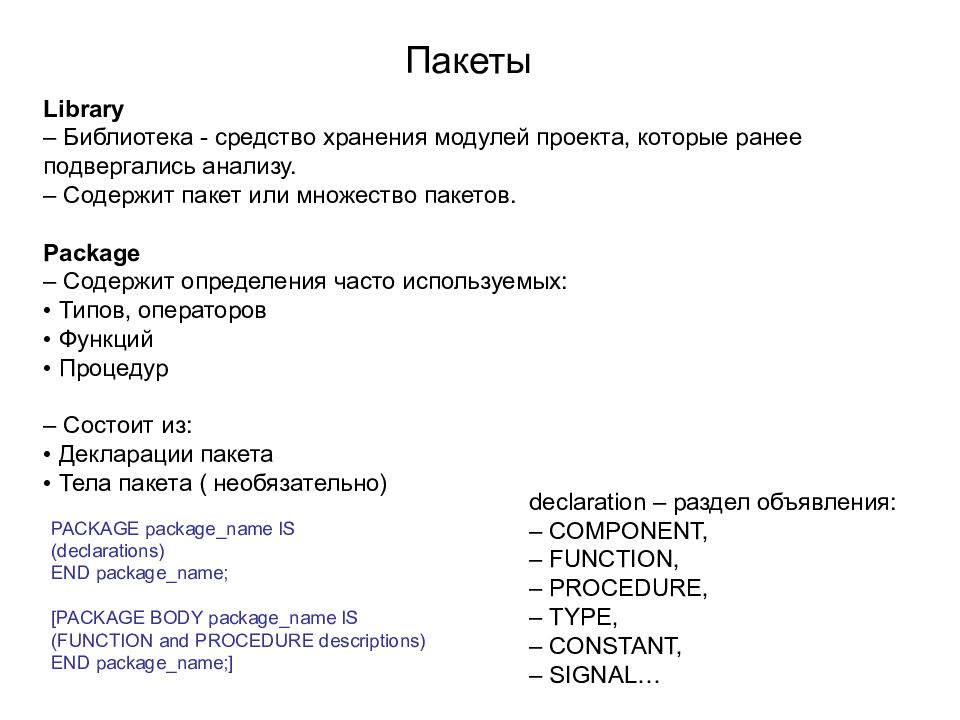

Слайд 33: Пакеты

Library – Библиотека - средство хранения модулей проекта, которые ранее подвергались анализу. – Содержит пакет или множество пакетов. Package – Содержит определения часто используемых: • Типов, операторов • Функций • Процедур – Состоит из: • Декларации пакета • Тела пакета ( необязательно) PACKAGE package_name IS (declarations) END package_name; [PACKAGE BODY package_name IS (FUNCTION and PROCEDURE descriptions) END package_name;] declaration – раздел объявления: – COMPONENT, – FUNCTION, – PROCEDURE, – TYPE, – CONSTANT, – SIGNAL…

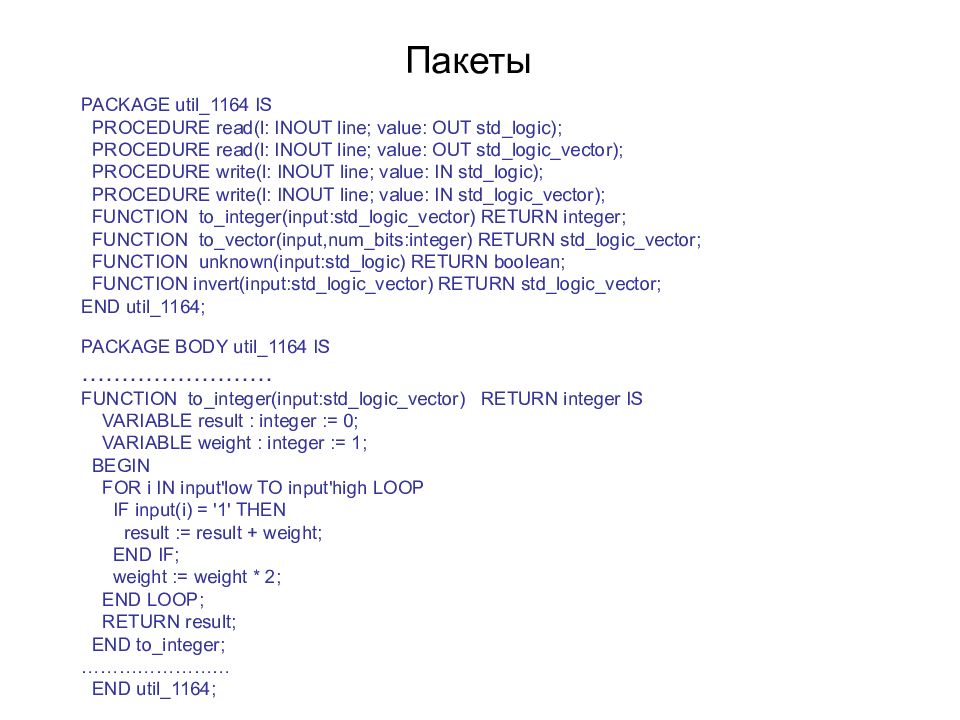

Последний слайд презентации: Основы языка VHDL Описание типовых дискретных устройств: Пакеты

PACKAGE util_1164 IS PROCEDURE read(l: INOUT line; value: OUT std_logic); PROCEDURE read(l: INOUT line; value: OUT std_logic_vector); PROCEDURE write(l: INOUT line; value: IN std_logic); PROCEDURE write(l: INOUT line; value: IN std_logic_vector); FUNCTION to_integer(input:std_logic_vector) RETURN integer; FUNCTION to_vector(input,num_bits:integer) RETURN std_logic_vector; FUNCTION unknown(input:std_logic) RETURN boolean; FUNCTION invert(input:std_logic_vector) RETURN std_logic_vector; END util_1164; PACKAGE BODY util_1164 IS …………………… FUNCTION to_integer(input:std_logic_vector) RETURN integer IS VARIABLE result : integer := 0; VARIABLE weight : integer := 1; BEGIN FOR i IN input'low TO input'high LOOP IF input(i) = '1' THEN result := result + weight; END IF; weight := weight * 2; END LOOP; RETURN result; END to_integer; …………………… END util_1164;