Первый слайд презентации: Вычислительные системы и телекоммуникации

Тема 3. Аппаратная платформа ПК (процессоры)

Слайд 2: План

Основные блоки ПК и их назначение. Микропроцессоры. CISC, RISC, VLIW. Физическая и функциональная структура микропроцессора. Устройство управления и Арифметико-логическое устройство. Микропроцессорная память. Интерфейсная часть МП.

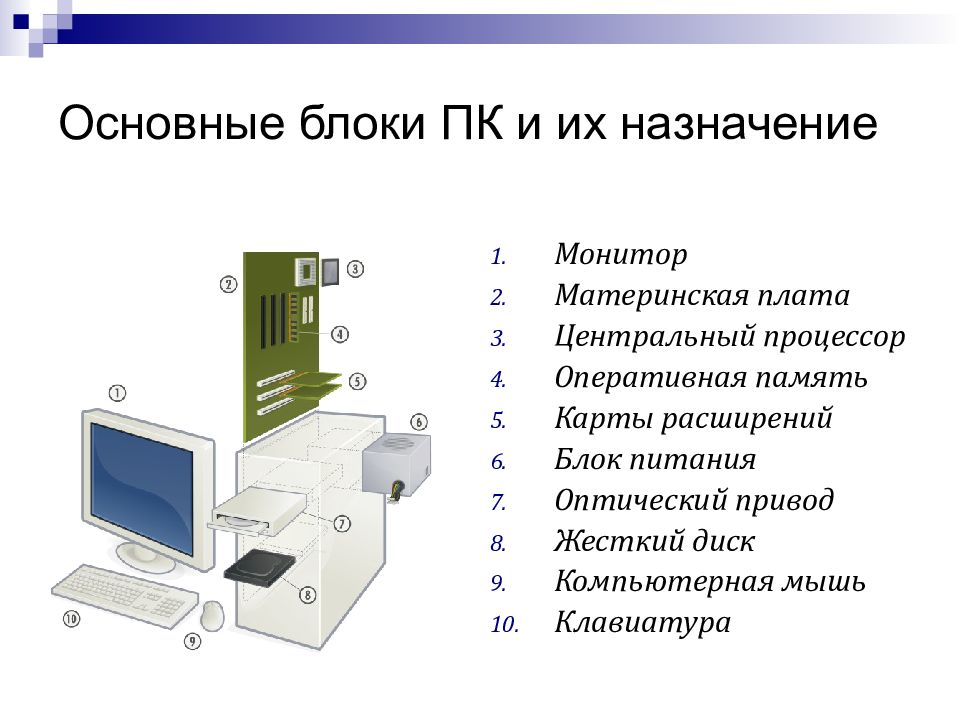

Слайд 3: Основные блоки ПК и их назначение

Монитор Материнская плата Центральный процессор Оперативная память Карты расширений Блок питания Оптический привод Жесткий диск Компьютерная мышь Клавиатура

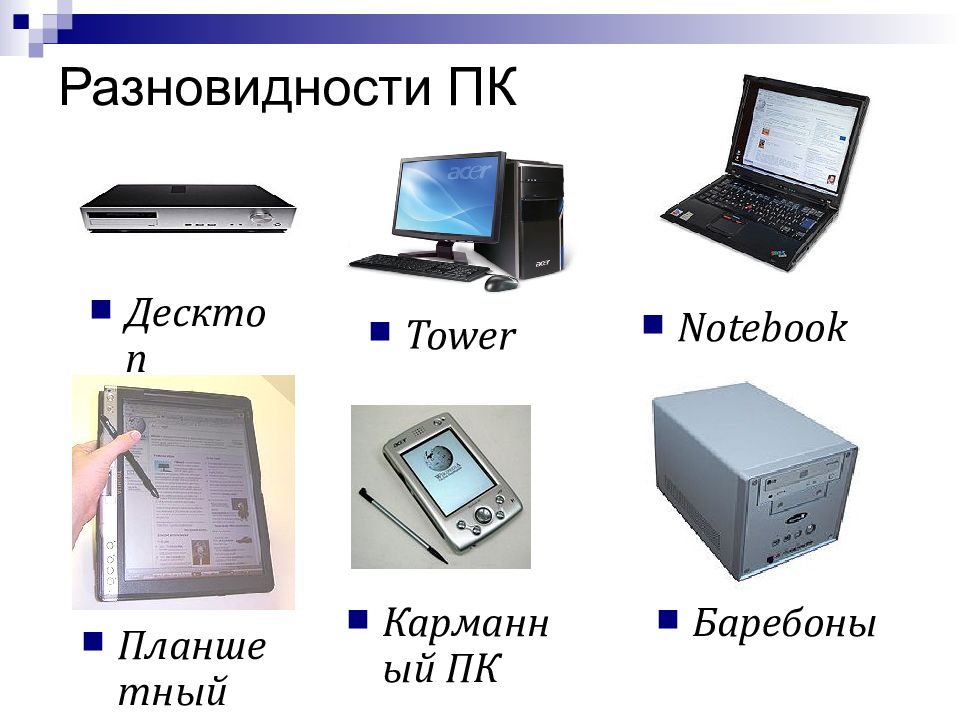

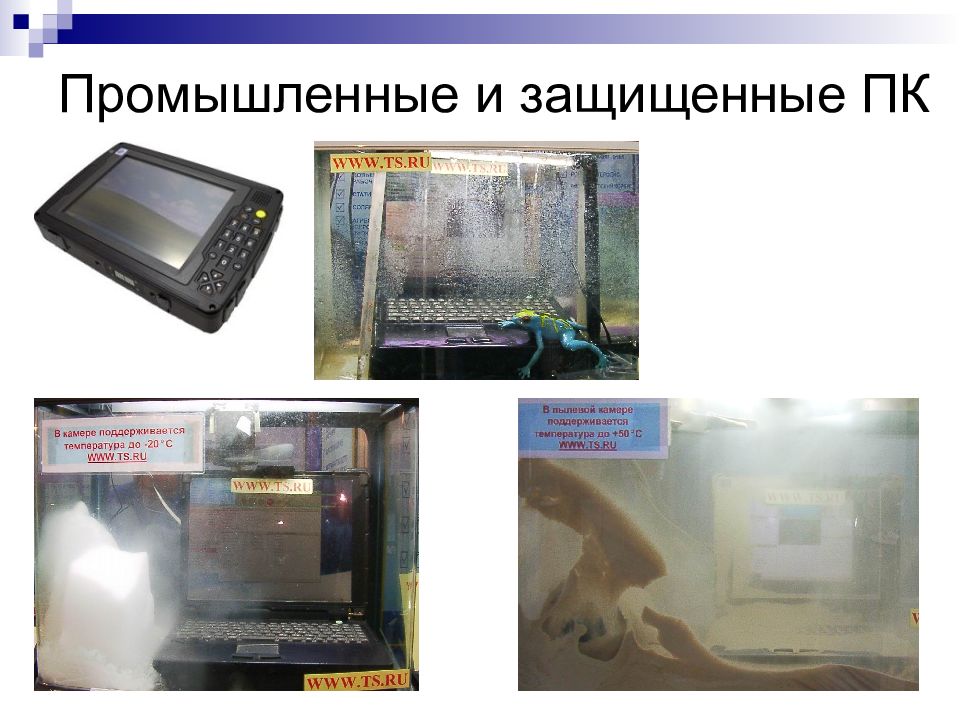

Слайд 5: Разновидности ПК

Десктоп Tower Notebook Планшетный Карманный ПК Баребоны

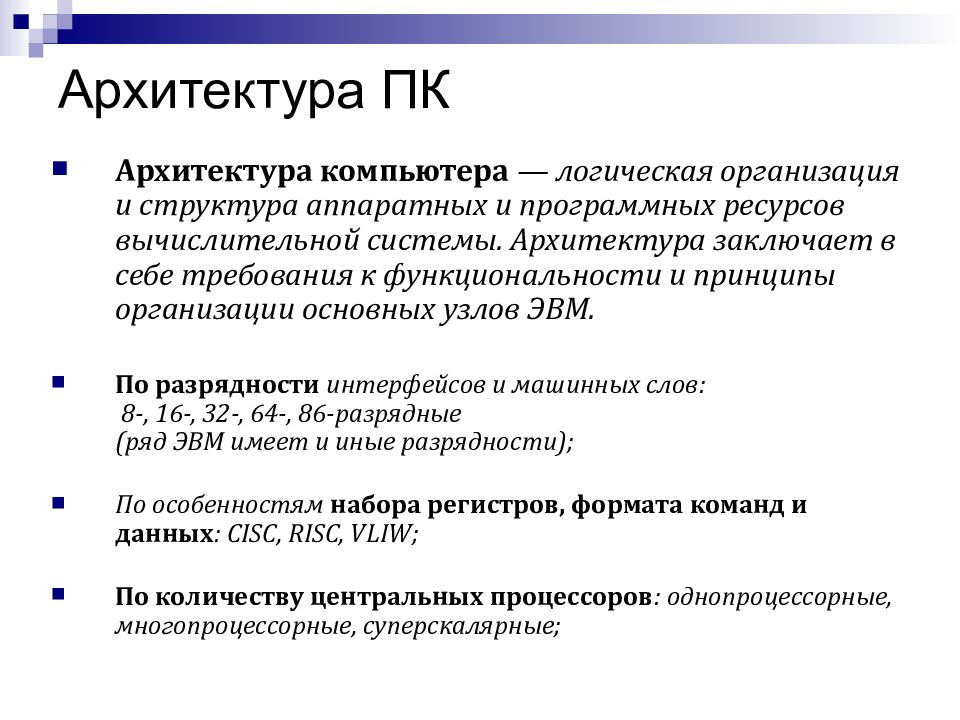

Слайд 7: Архитектура ПК

Архитектура компьютера — логическая организация и структура аппаратных и программных ресурсов вычислительной системы. Архитектура заключает в себе требования к функциональности и принципы организации основных узлов ЭВМ. По разрядности интерфейсов и машинных слов: 8-, 16-, 32-, 64-, 86-разрядные (ряд ЭВМ имеет и иные разрядности); По особенностям набора регистров, формата команд и данных : CISC, RISC, VLIW; По количеству центральных процессоров : однопроцессорные, многопроцессорные, суперскалярные;

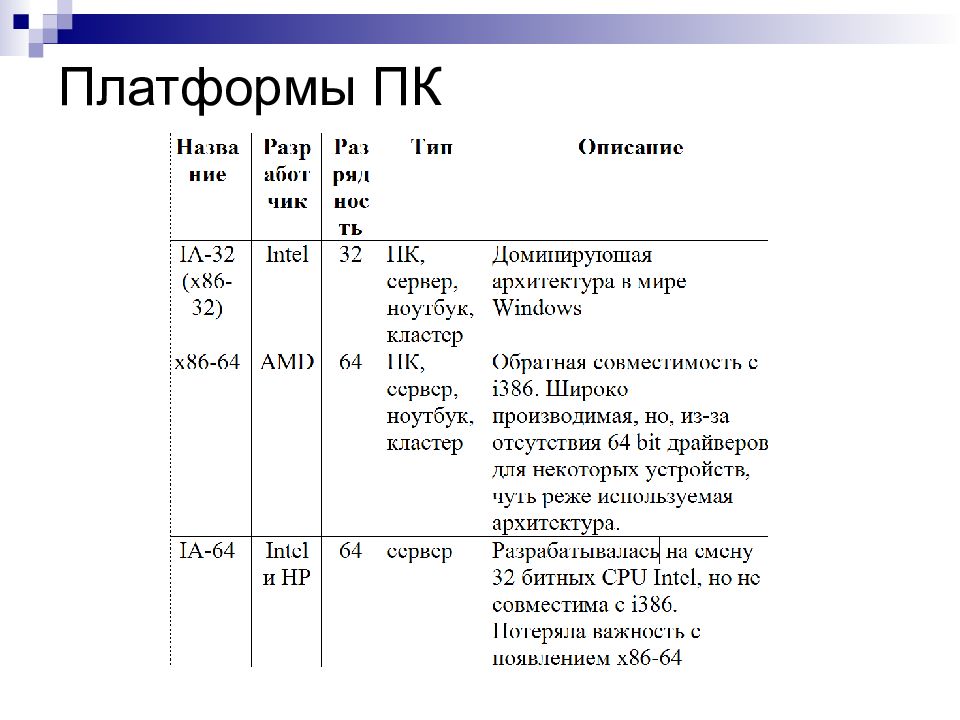

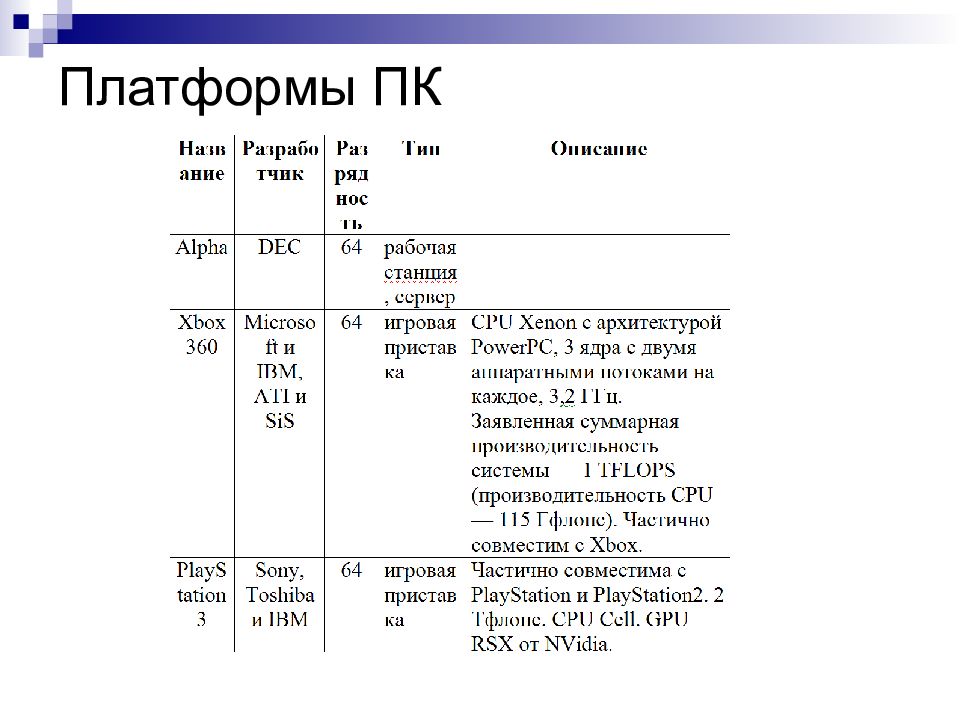

Слайд 9: Платформа ПК

Аппаратная платформа компьютера является нижним слоем многоуровневой организации компьютера, на который опираются ОС и прикладное ПО. Аппаратные платформы отличаются друг от друга процессором, чипсетом и другими компонентами материнской платы. Каждая аппаратная платформа имеет список ОС и прикладных программ, которые могут на ней запускаться. Приложения Операционная система ЦП Память Устройства Аппаратная платформа Программная платформа

Слайд 12: Совместимость платформ

Большинство аппаратных платформ ПК являются несовместимыми из-за различия команд процессора, а так же различия системных шин и т.п. устройств на материнской плате. Проблема совместимости процессоров - ситуация, когда 2 процессора не могут выполнять один и тот же машинный код. Например, Pentium и Pentium 2 — два 32-битных процессора Intel. Между ними то же может возникнуть несовместимость. Pentium по причине отсутствия MMX команд не справится с программой, откомпилированной для Pentium 2. Примером несовместимости на уровне команд процессора являются, платформы Intel: IA-64 и x86-64.

Слайд 13: Платформа x86-64 (AMD64 / Intel64 / EM64T / x64)

x86-64 (AMD64/Intel64/EM64T/x64) 64-битн ая аппаратная платформа: архитектура микропроцессора и соответствующий набор инструкций и чипсет, разработанные компанией AMD. Это расширение архитектуры x86 с полной обратной совместимостью. Набор инструкций x86-64 в настоящее время поддерживается процессорами AMD Athlon 64, Athlon 64 FX, Athlon 64 X2, Phenom, Phenom II, Turion 64, Opteron, последними моделями Sempron. Этот набор инструкций был поддержан основным конкурентом AMD — компанией Intel (с незначительными дополнениями) под названием Intel 64 (ранее известные как EM64T и IA-32e ) в поздних моделях процессоров Pentium 4, а также в Pentium D, Pentium Extreme Edition, Celeron D, Core 2 Duo, Core 2 Quad и Xeon. Разработанный компанией AMD набор инструкций x86-64 (позднее переименованный в AMD64) — расширение архитектуры Intel IA-32 (x86-32). Основной отличительной особенностью AMD64 является поддержка 16-ти 64-битных регистров общего назначения (против 8-и 32-битных в x86-32), 64-битных арифметических и логических операций над целыми числами и 64-битных виртуальных адресов.

Слайд 14: Платформа x86-64 (AMD64/Intel64/EM64T/x64)

Существует несколько вариантов названий этой технологии, которые, порой, приводят к путанице и могут ввести в заблуждение. x86-64. Первоначальный вариант. Именно под этим названием фирмой AMD была опубликована первая предварительная спецификация. AA-64. Так архитектуру окрестил популярный неофициальный справочник sandpile.org (внеся информацию практически сразу после публикаций первой предварительной спецификации) по аналогии с IA-64, и по-прежнему так её называющий, как AMD Architecture 64. AMD64. После выпуска первых Hammer’ов в названии архитектуры появилось название фирмы-разработчика Advanced Micro Devices. Сейчас является официальным для реализации AMD. Yamhill Tehnology. Первое название Intel'овской реализации технологии. Иногда упоминалось название CT (Clackamas Technology). EM64T. Первое официальное название реализации Intel. Расшифровывалось как Extended Memory 64 Technology. IA-32e. Иногда встречалось совместно с EM64T, чаще для обозначения длинного режима, который в документации Intel называется "режимом IA-32e". Intel 64. Текущее официальное название архитектуры Intel. Постепенно Intel отказывается от наименований IA-32, IA-32e и EM64T в пользу этого названия, которое теперь является единственным официальным для этой архитектуры. x64 Официальное название версий операционных систем Windows и Solaris, также используемое как название архитектуры фирмами Microsoft и Sun Microsystems.

Слайд 15: Режимы работы процессоров х64

Процессоры архитектуры x86-64 поддерживают два режима работы: Long mode («длинный» режим) Legacy mode («наследственный», режим совместимости с x86). Long Mode - «Длинный» режим — «родной» для процессоров AMD64. Этот режим позволяет воспользоваться всеми дополнительными возможностями, предоставляемыми архитектурой AMD64. Для использования этого режима необходима 64-битная операционная система, например, Windows XP Professional x64 Edition, Windows Vista x64, Windows7x64 или 64-битные варианты UNIX-подобных систем GNU/Linux Long Mode режим позволяет выполнять 64-битные программы ; также (для обратной совместимости) предоставляется поддержка выполнения 32-битного кода, например, 32-битных приложений, хотя 32-битные программы не смогут использовать 64-битные системные библиотеки, и наоборот. Чтобы справиться с этой проблемой, большинство 64-разрядных операционных систем предоставляют два набора необходимых системных файлов: один — для родных 64-битных приложений, и другой — для 32-битных программ.

Слайд 16: Режимы работы процессоров х64

Legacy Mode- Данный «наследственный» режим позволяет процессору AMD64 выполнять инструкции, рассчитанные для процессоров x86, и предоставляет полную совместимость с 32/16-битным кодом и операционными системами. В этом режиме процессор ведёт себя точно так же, как x86-процессор, например Pentium 4, и дополнительные функции, предоставляемые архитектурой AMD64 (например, дополнительные регистры) недоступны. В этом режиме 64-битные программы и операционные системы работать не будут (если, конечно, не используется виртуализация).

Слайд 17: Центральный процессор

Центра́льный проце́ссор (ЦП; central processing unit, CPU, дословно — центральное вычислительное устройство) — исполнитель машинных инструкций, часть аппаратного обеспечения компьютера или программируемого логического контроллера, отвечающий за выполнение операций, заданных программами. Современные ЦП, выполняются в виде отдельных микросхем (чипов), реализующих все особенности, присущие данного рода устройствам, называют микропроцессорами.

Слайд 18: Центральный процессор

Основными техническими характеристиками процессора в настоящее время считаются: Архитектура системы команд процессора Модель процессора, связанная с его системой команд Внутренняя тактовая частота Разрядность и длинна машинного слова Объем внутреннего кэша L1 Производительность Плотность логических элементов Линейный размер логических элементов Форм-фактор

Слайд 19: Микроархитектура процессора

Идею микропрограммирования с целью упрощения аппаратного обеспечения компьютера предложил в 1951 году М. Уилкс из Кембриджа. Он предложил включить в структурную организацию ПК между цифровым логическим уровнем и уровнем машинных команд включить дополнительный микроархитектурный уровень. Основу микроархитектурного уровня образуют микрокоманды Каждая микрокоманда, выдавая управляющие сигналы на отдельные вентили аппаратных схем, определяет некоторое простейшее действие процессора, например задает выбор кода из регистра процессора, установка флага. Выполнение любой машинной команды фактически представляет собой выполнение соответствующей последовательности микрокоманд.

Слайд 20: Принципы работы ЦП, процесс

Большинство современных процессоров для персональных компьютеров в общем основаны на той или иной версии циклического процесса последовательной обработки информации, изобретённого Джоном фон Нейманом. Этапы цикла(процесса) выполнения: Процессор выставляет число, хранящееся в регистре счётчика команд, на шину адреса, и отдаёт памяти команду чтения; Выставленное число является для памяти адресом ; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных, и сообщает о готовности; Процессор получает число с шины данных, интерпретирует его как команду ( машинную инструкцию ) из своей системы команд и исполняет её; Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счётчике команд; в результате там образуется адрес следующей команды; Снова выполняется п. 1.

Слайд 21: Принципы работы ЦП, процесс

Команды центрального процессора являются самым нижним уровнем управления компьютером, поэтому выполнение каждой команды неизбежно и безусловно. Не производится никакой проверки на допустимость выполняемых действий, в частности, не проверяется возможная потеря ценных данных. Чтобы компьютер выполнял только допустимые действия, команды должны быть соответствующим образом организованы в виде необходимой программы. Скорость перехода от одного этапа цикла к другому определяется тактовым генератором. Тактовый генератор вырабатывает импульсы, служащие ритмом для центрального процессора. Частота тактовых импульсов называется тактовой частотой.

Слайд 22: Виды микропроцессоров ПК CISC, RISC, MISC, VLiW

CISC ( Complex Instruction Set Computer ) — вычисления со сложным набором команд RISC ( Reduced Instruction Set Computer ) — вычисления с сокращённым набором команд MISC ( Minimum Instruction Set Computer ) — вычисления с минимальным набором команд. VLiW - суперскалярные

Слайд 23: CISC-процессоры

Complex Instruction Set Computer — вычисления со сложным набором команд. Процессорная архитектура, основанная на усложнённом наборе команд. Типичными представителями CISC является семейство микропроцессоров Intel x86 (хотя уже много лет эти процессоры являются CISC только по внешней системе команд). CISC— концепция проектирования процессоров, которая характеризуется следующим набором свойств: • Нефиксированным значением длины команды. • Арифметические действия кодируются в одной инструкции. • Небольшим числом регистров, каждый из которых выполняет строго определённую функцию.

Слайд 25: CISC-процессоры

Формально, все х86-процессоры являлись CISC-процессорами ( Complete Instruction Set Computer ) IBM360/370, VAX, Intel 80x86 Для архитектуры CISC характерно: Небольшое количество регистров общего назначения Большое количество различных машинных команд, каждая из которых выполняется за несколько тактов процессора Различные форматы команд с разной длинной Преобладание двухадресной адресации Развитый механизм адресации операндов

Слайд 26: CISC-процессоры

Процессоры, начиная с Intel486DX, являются CISC-процессорами с RISC-ядром. Они непосредственно перед исполнением преобразуют CISC-инструкции процессоров x86 в более простой набор внутренних инструкций RISC. В микропроцессор встраивается аппаратный транслятор, превращающий команды x86 в команды внутреннего RISC-процессора. При этом одна команда x86 может порождать несколько RISC-команд (в случае процессоров типа P6 — до 4-х RISC команд в большинстве случаев). Исполнение команд происходит на суперскалярном конвейере одновременно по несколько штук. Это потребовалось для увеличения скорости обработки CISC-команд, так как известно, что любой CISC-процессор уступает RISC-процессорам по количеству выполняемых операций в секунду. В итоге, такой подход и позволил поднять производительность CPU.

Слайд 28: RISC-процессоры

Reduced Instruction Set Computer — вычисления с сокращённым набором команд. Характеризуется наличием команд фиксированной длины, большого количества регистров, операций типа регистр-регистр, а также отсутствием косвенной адресации. Среди первых были процессоры MIPS, PowerPC, SPARC, Alpha, PA-RISC. В мобильных устройствах широко используются ARM-процессоры. RISC Это концепция проектирования процессоров (ЦПУ), которая во главу ставит следующий принцип: более компактные и простые инструкции выполняются быстрее. Простая архитектура позволяет удешевить процессор, поднять тактовую частоту, а также распараллелить исполнение команд между несколькими блоками исполнения (т. н. суперскалярные архитектуры процессоров).

Слайд 29: RISC-процессоры

Идея создания RISC процессоров пришла после того, как в 1970-х годах ученые из IBM обнаружили, что многие из функциональных особенностей традиционных ЦПУ игнорировались программистами. Отчасти это был побочный эффект сложности компиляторов. В то время компиляторы могли использовать лишь часть из набора команд процессора. Следующее открытие заключалось в том, что, поскольку некоторые сложные операции использовались редко, они как правило, были медленнее, чем те же действия, выполняемые набором простых команд. Это происходило из-за того, что создатели процессоров тратили гораздо меньше времени на улучшение сложных команд, чем на улучшение простых.

Слайд 30: Для RISC-процессоров характерно:

Большое количество регистров в составе процессора Упрощение и сокращение набора команд Одинаковый формат для большинства команд Одна и таже разрядность для всех команд Выполнение командами простых действий, как правило за один такт Использование для обрабатывающих команд только регистровой адресации Использование простых способов адресации Минимизация времени выполнения команд К RISC архитектуре относятся семейства SUN SPARC, Alpha, PowerPC,MIPS.

Слайд 31: Архитектурные решения, типичные для RISC

Спекулятивное исполнение. При встрече с командой условного перехода процессор исполняет (или по крайней мере читает в кэш инструкций) сразу обе ветви, до тех пор, пока не окончится вычисление управляющего выражения перехода. Позволяет отказаться от простоев конвейера при условных переходах. Переименование регистров. Каждый регистр процессора на самом деле представляет собой несколько параллельных регистров, хранящих несколько версий значения. Используется для реализации спекулятивного исполнения.

Слайд 32: MISC-процессоры

Minimum Instruction Set Computer — вычисления с минимальным набором команд. Архитектура MISC строится на стековой вычислительной модели с ограниченным числом команд (примерно 20-30 команд). Основная идея — сильно упростив внутреннее устройство процессора и используя очень длинный (по тем временам) конвейер, можно получить процессор, не умеющий выполнять сравнительно сложные инструкции, зато работающий на очень высоких тактовых частотах, позволяющих скомпенсировать потери производительности на эмуляцию этих сложных инструкций. Изначально предполагалось, что MIPS-процессоры не будут аппаратно поддерживать даже операции умножения и деления, благодаря чему можно было обойтись без сложных в реализации блокировок конвейера.

Слайд 33: Процессоры конвейерной арх

Конвейерная архитектура (pipelining) была введена в центральный процессор с целью повышения быстродействия. Впервые параллелизм на уровне команд был реализован в архитектуре машины IBM Streth 1961 г. В её конструкции был использован буфер вызова команд с упреждением. Обычно для выполнения каждой команды требуется осуществить некоторое количество однотипных операций, например: выборка команды из ОЗУ, дешифрация команды, адресация операнда в ОЗУ, выборка операнда из ОЗУ, выполнение команды, запись результата в ОЗУ. Каждую из этих операций сопоставляют одной ступени конвейера. Например, конвейер микропроцессора с архитектурой MIPS-I «микропроцессор без блокировок в конвейере») содержит четыре стадии: получение и декодирование инструкции ( Fetch ) адресация и выборка операнда из ОЗУ ( Memory access ) выполнение арифметических операций ( Arithmetic Operation ) сохранение результата операции ( Store )

Слайд 34: Конвейерная архитектура

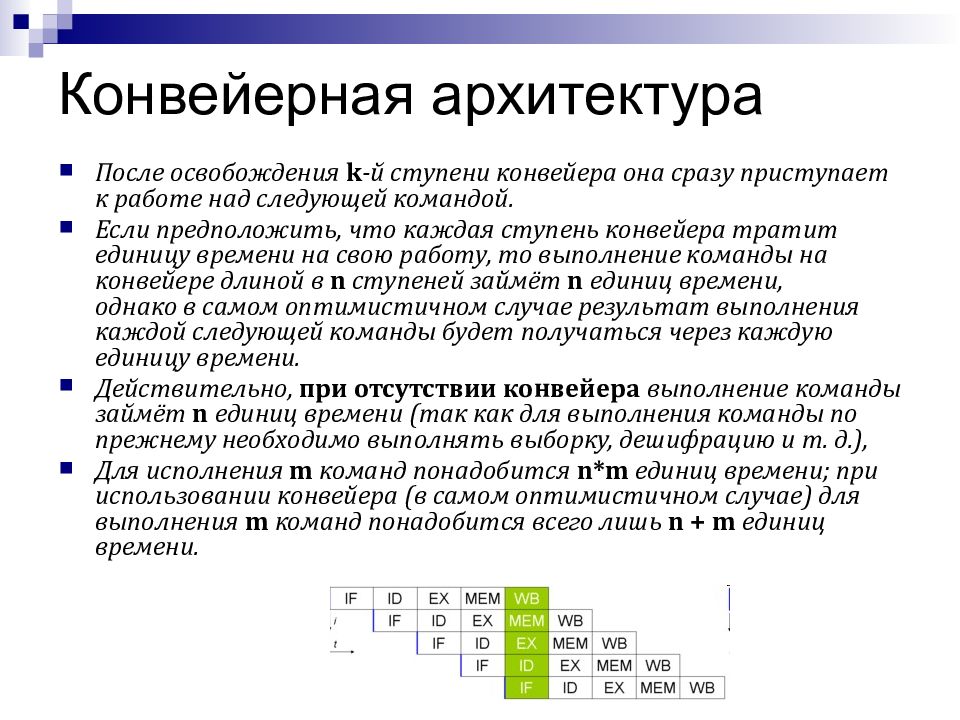

После освобождения k -й ступени конвейера она сразу приступает к работе над следующей командой. Если предположить, что каждая ступень конвейера тратит единицу времени на свою работу, то выполнение команды на конвейере длиной в n ступеней займёт n единиц времени, однако в самом оптимистичном случае результат выполнения каждой следующей команды будет получаться через каждую единицу времени. Действительно, при отсутствии конвейера выполнение команды займёт n единиц времени (так как для выполнения команды по прежнему необходимо выполнять выборку, дешифрацию и т. д.), Для исполнения m команд понадобится n*m единиц времени; при использовании конвейера (в самом оптимистичном случае) для выполнения m команд понадобится всего лишь n + m единиц времени.

Слайд 35: Принципы конвейерной обработки

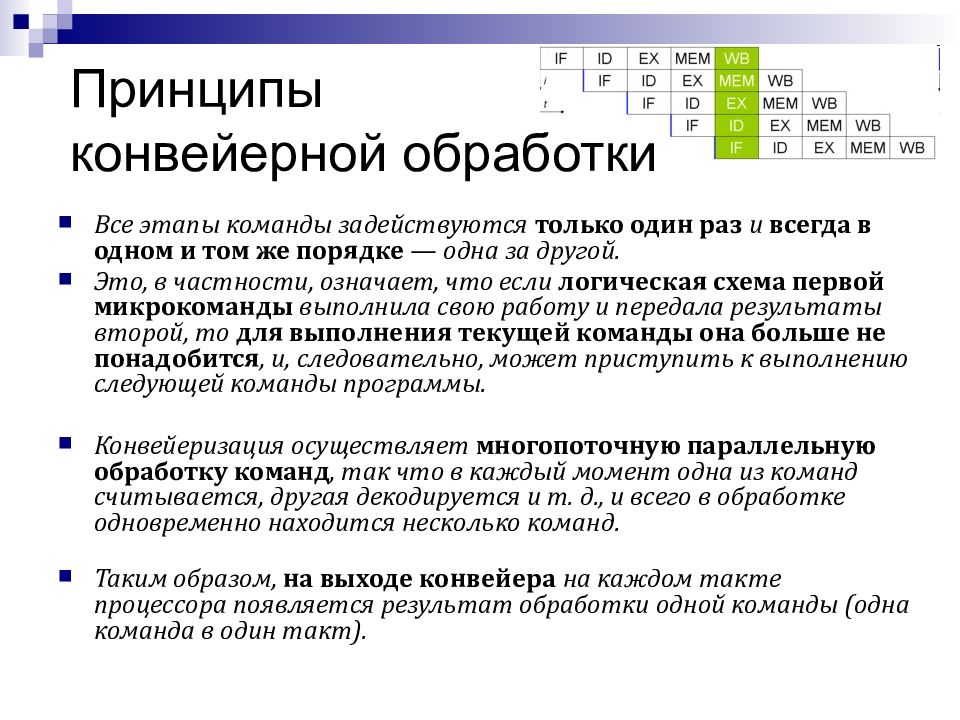

Все этапы команды задействуются только один раз и всегда в одном и том же порядке — одна за другой. Это, в частности, означает, что если логическая схема первой микрокоманды выполнила свою работу и передала результаты второй, то для выполнения текущей команды она больше не понадобится, и, следовательно, может приступить к выполнению следующей команды программы. Конвейеризация осуществляет многопоточную параллельную обработку команд, так что в каждый момент одна из команд считывается, другая декодируется и т. д., и всего в обработке одновременно находится несколько команд. Таким образом, на выходе конвейера на каждом такте процессора появляется результат обработки одной команды (одна команда в один такт).

Слайд 36: Принципы конвейерной обработки

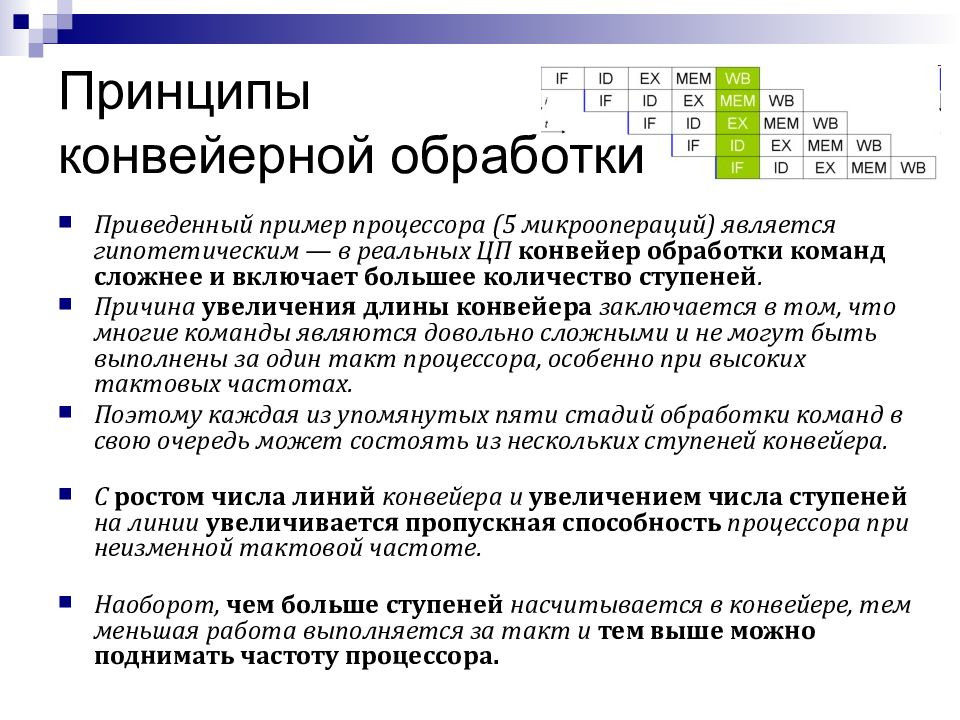

Приведенный пример процессора (5 микроопераций) является гипотетическим — в реальных ЦП конвейер обработки команд сложнее и включает большее количество ступеней. Причина увеличения длины конвейера заключается в том, что многие команды являются довольно сложными и не могут быть выполнены за один такт процессора, особенно при высоких тактовых частотах. Поэтому каждая из упомянутых пяти стадий обработки команд в свою очередь может состоять из нескольких ступеней конвейера. С ростом числа линий конвейера и увеличением числа ступеней на линии увеличивается пропускная способность процессора при неизменной тактовой частоте. Наоборот, чем больше ступеней насчитывается в конвейере, тем меньшая работа выполняется за такт и тем выше можно поднимать частоту процессора.

Слайд 37: Факторы, снижающие эффективность конвейера

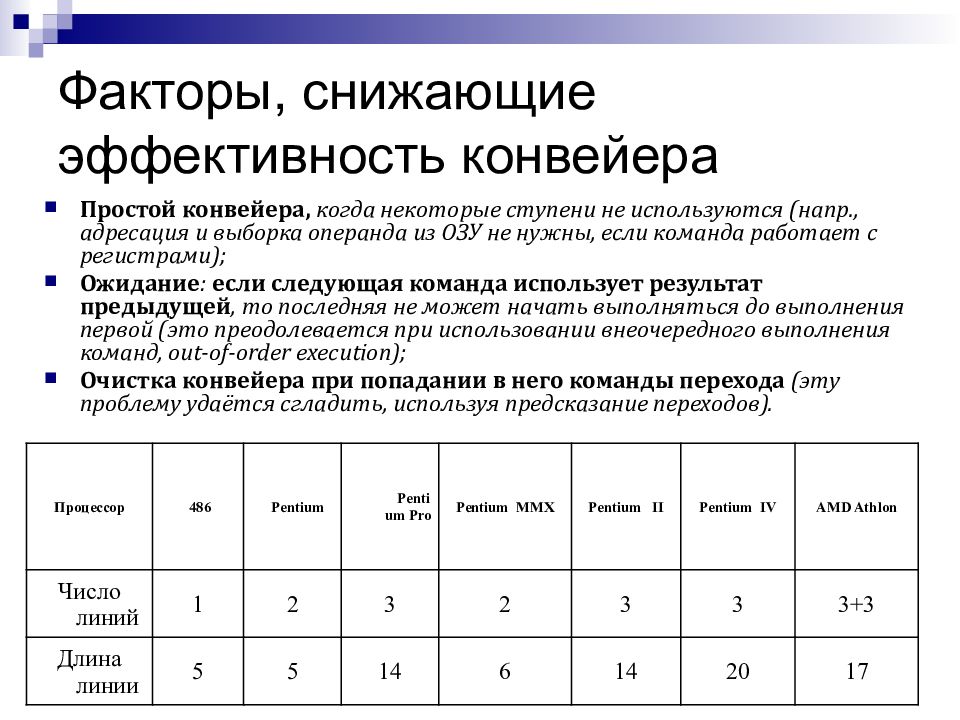

Простой конвейера, когда некоторые ступени не используются (напр., адресация и выборка операнда из ОЗУ не нужны, если команда работает с регистрами); Ожидание : если следующая команда использует результат предыдущей, то последняя не может начать выполняться до выполнения первой (это преодолевается при использовании внеочередного выполнения команд, out-of-order execution); Очистка конвейера при попадании в него команды перехода (эту проблему удаётся сгладить, используя предсказание переходов). Процессор 486 Pentium Pentium Pro Pentium MMX Pentium II Pentium IV AMD Athlon Число линий 1 2 3 2 3 3 3+3 Длина линии 5 5 14 6 14 20 17

Слайд 38: Архитектура процессоров конвейерной обработки

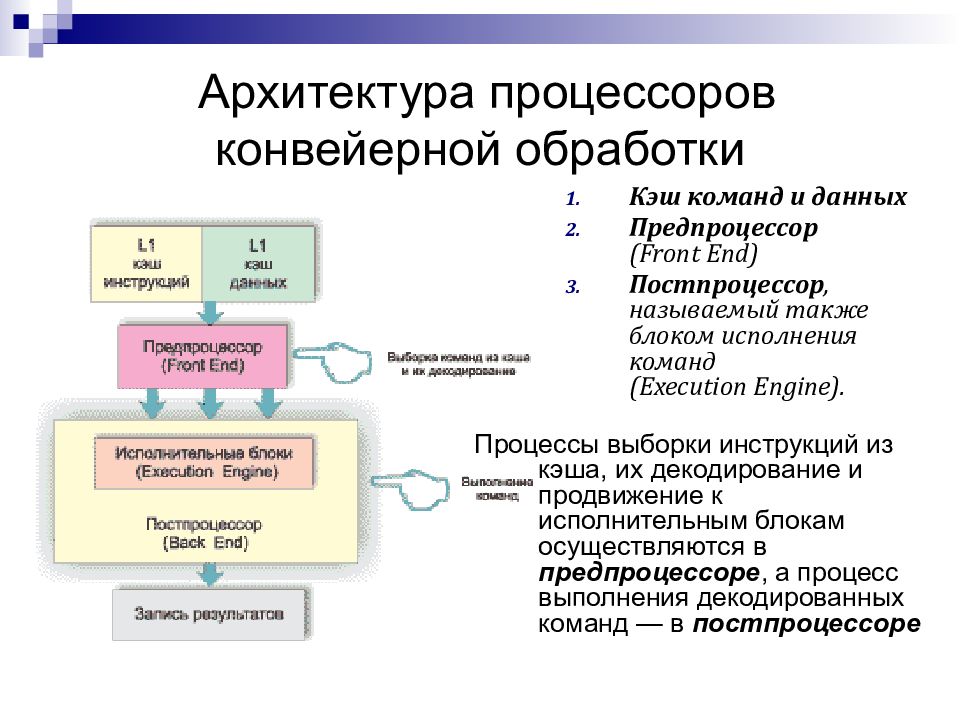

Кэш команд и данных Предпроцессор (Front End) Постпроцессор, называемый также блоком исполнения команд (Execution Engine). Процессы выборки инструкций из кэша, их декодирование и продвижение к исполнительным блокам осуществляются в предпроцессоре, а процесс выполнения декодированных команд — в постпроцессоре

Слайд 39: Процесс обработки данных

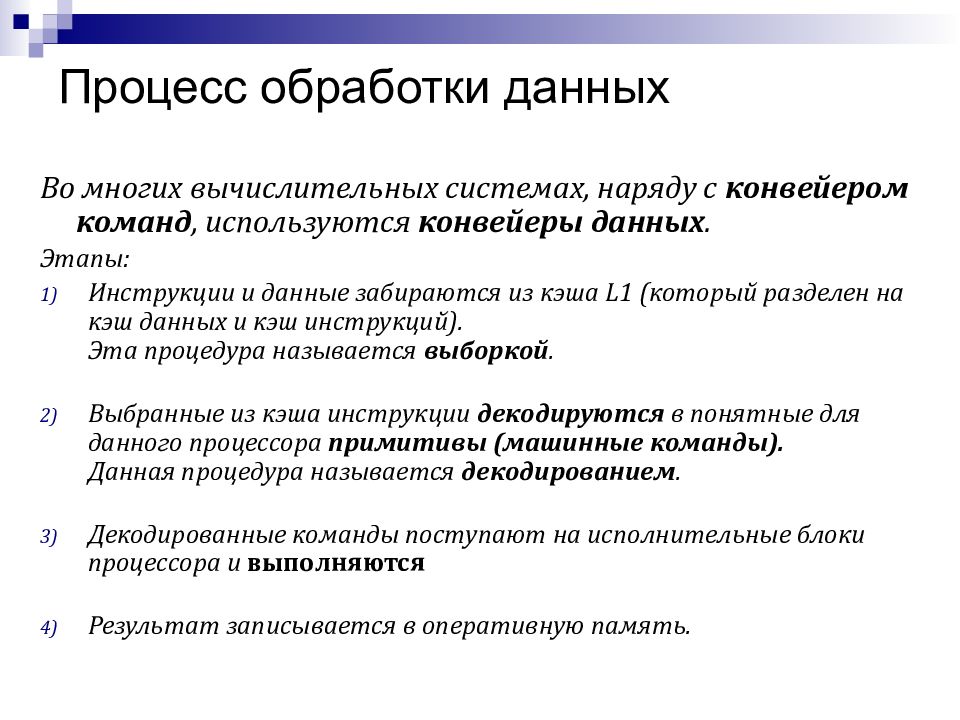

Во многих вычислительных системах, наряду с конвейером команд, используются конвейеры данных. Этапы: Инструкции и данные забираются из кэша L1 (который разделен на кэш данных и кэш инструкций). Эта процедура называется выборкой. Выбранные из кэша инструкции декодируются в понятные для данного процессора примитивы (машинные команды). Данная процедура называется декодированием. Декодированные команды поступают на исполнительные блоки процессора и выполняются Результат записывается в оперативную память.

Слайд 40: 2 подхода к повышению производительности

Всякий процессор должен быть сконструирован таким образом, чтобы за минимальное время выполнять максимальное количество инструкций. количество выполняемых за единицу времени инструкций и определяет производительность процессора. Существует два принципиально различных подхода к повышению производительности процессора (не считая, конечно, увеличения тактовой частоты). ПЕРВЫЙ: за счет уменьшения длины конвейера увеличивать количество исполнительных блоков. ВТОРОЙ: за счет длинного конвейера возможно увеличение тактовой частоты процессора, то есть сам конвейер оказывается более быстрым.

Слайд 41: Короткий конвейер

«Короткий конвейер» позволяет в полной мере реализовать параллелизм на уровне инструкций (Instruction-Level Parallelism, ILP), когда несколько инструкций выполняются одновременно в различных исполнительных блоках процессора. Однако если, к примеру, для выполнения следующей по порядку инструкции требуется знать результат выполнения предыдущей инструкции (взаимозависимые инструкции), то в этом случае параллельное выполнение невозможно. Поэтому препроцессор прежде всего проверяет взаимозависимость команд и переупорядочивает их не в порядке поступления (out of order), а так, чтобы их можно было выполнять параллельно. На последних ступенях конвейера инструкции выстраиваются в исходном порядке. Важно, что количество ступеней конвейера внутри постпроцессора (исполнительного блока) здесь невелико, поэтому инструкции выполняются за небольшое количество циклов. Идея: за счет уменьшения длины конвейера увеличивать количество исполнительных блоков. Таким образом, по существу реализуется множество параллельных коротких конвейеров.

Слайд 42: Длинный конвейер

С учетом того, что каждая ступень выполняется за один процессорный такт, длинные конвейеры позволяют повышать тактовые частоты процессора, что невозможно в случае коротких конвейеров. При использовании длинного конвейера возможно увеличение тактовой частоты процессора, то есть сам конвейер оказывается более быстрым. В случае длинного конвейера постпроцессора предпроцессору необходимо обеспечивать его соответствующую загрузку. Для этого предпроцессор должен обладать довольно большим буфером, способным вмещать достаточное количество инструкций. Если же в кэше L1 отсутствует инструкция или данные для конвейера, то образуются так называемые pipeline bubbles (конвейерные пузырьки). Идея: Чем больше количество ступеней, на которые разбит конвейер, тем меньшее количество работы выполняется на каждой ступени и, следовательно, тем меньше времени требуется для прохождения командой данной ступени.

Слайд 43: Суперскалярные процессоры VLIW

Суперскалярность — архитектура вычислительного ядра, использующая несколько декодеров команд, которые могут нагружать работой множество исполнительных блоков. Суперскаляризация. Процессоры с несколькими линиями конвейера получили название суперскалярных. Pentium — первый суперскалярный процессор Intel. Здесь две линии, что позволяет ему при одинаковых частотах быть вдвое производительней i 80486, выполняя сразу две инструкции за такт. Планирование исполнения потока команд является динамическим и осуществляется самим вычислительным ядром. Если в процессе работы команды, обрабатываемые конвейером, не противоречат друг другу, и одна не зависит от результата другой, то такое устройство может осуществить параллельное выполнение команд.

Слайд 44: Суперскалярные процессоры VLIW

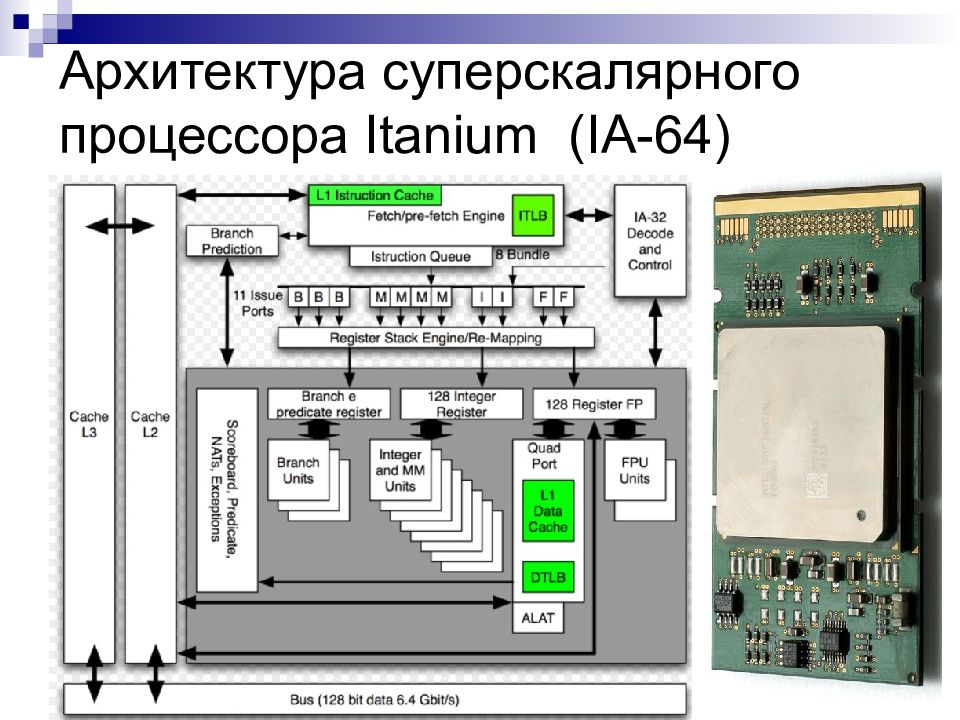

Vliw (Very large Instruction Word) – очень длинное командное слово является разновидностью RISC архитектуры. В суперскалярных системах решение о запуске инструкции на исполнение принимает сам вычислительный модуль, что требует много ресурсов. В более продвинутых системах, таких как Эльбрус-3 и Itanium, используется статпланирование, то есть параллельные инструкции объединяются компилятором в длинную команду, в которой все инструкции заведомо параллельные (архитектура VLIW). Процессоры с несколькими линиями конвейера получили название суперскалярных. Pentium — первый суперскалярный процессор Intel. Здесь две линии, что позволяет ему при одинаковых частотах быть вдвое производительней i80486, выполняя сразу две инструкции за такт.

Слайд 47: Операции над вещественными числами (с плавающей запятой)

Сопроцессоры. Для расширения вычислительных возможностей центрального процессора — выполнения арифметических операций, вычисления основных математических функций (тригонометрических, показательных, логарифмических) и т. д. — в состав ЭВМ добавляется математический сопроцессор. Применение сопроцессора повышает производительность вычислений в сотни раз. В разных поколениях процессоров он назывался по-разному — FPU ( Floating Point Unit — блок чисел/операций с плавающей точкой - БПЗ) или NPX (Numeric Processor extension — числовое расширение процессора). Для процессоров 386 и ниже сопроцессор был отдельной микросхемой, подключаемой к локальной нише основного процессора. В любом случае сопроцессор исполняет только свои специфические команды, а всю работу по декодированию инструкций и доставке данных осуществляет ЦП. С программной точки зрения сопроцессор и процессор выглядят как единое целое. В (486+) процессорах БПЗ располагается на одном кристалле с центральным процессором

Слайд 48: Динамическое исполнение (dynamic execution technology)

Динамическое исполнение - технология обработки данных процессором, обеспечивающая более эффективную работу процессора за счет манипулирования данными, а не просто линейного исполнения списка инструкций. Предсказание ветвлений. С большой точностью (более 90 %) процессор предсказывает, в какой области памяти можно найти следующие инструкции. Это оказывается возможным, поскольку в процессе исполнения инструкции процессор просматривает программу на несколько шагов вперед. Это обеспечивает значительное повышение производительности. Например, программный цикл, состоящий из пересылки, сравнения, сложения и перехода в 80486 DX, выполняется за шесть тактов синхронизации, а в — Pentium за два (команды пересылки и сложения, а также сравнения и перехода сочетаются и предсказывается переход).

Слайд 49: Динамическое исполнение (dynamic execution technology)

Внеочередное выполнение (выполнение вне естественного порядка — out-of-order execution). Процессор анализирует поток команд и составляет график исполнения инструкций в оптимальной последовательности, независимо от порядка их следования в тексте программы, просматривая декодированные инструкции и определяя, готовы ли они к непосредственному исполнению или зависят от результата других инструкций. Далее процессор определяет оптимальную последовательность выполнения и исполняет инструкции наиболее эффективным образом. Переименование (ротация) регистров (register rename). Чтобы избежать пересылок данных между регистрами в соответствующей команде изменяется адрес регистра, содержащего данные, участвующие в следующей операции. Поэтому вместо пересылки данных в регистр-источник осуществляется трактовка регистра с данными как источника.

Слайд 50: Динамическое исполнение (dynamic execution technology)

Выполнение по предположению ( спекулятивное — speculative). Процессор выполняет инструкции (до пяти инструкций одновременно) по мере их поступления в оптимизированной последовательности (спекулятивно). Поскольку выполнение инструкций происходит на основе предсказания ветвлений, результаты сохраняются как предположительные («спекулятивные»). На конечном этапе порядок инструкций восстанавливается. Предикация (predication) — одновременное исполнение нескольких ветвей программы вместо предсказания переходов (выполнения наиболее вероятного); При использовании предикации компилятор, обнаружив оператор ветвления в исходной программе, анализирует все возможные ветви (блоки) и помечает их метками или предикатами (predicate). После этого он определяет, какие из них могут быть выполнены параллельно (из соседних, независимых ветвей).

Слайд 51: Динамическое исполнение (dynamic execution technology)

Предикация. Обычный компилятор транслирует оператор ветвления (например, IF-THEN-ELSE) В блоки машинного кода, расположенные последовательно в потоке. Обычный процессор, в зависимости от исхода условия, исполняет один из этих базовых блоков, пропуская все другие. Более развитые процессоры пытаются прогнозировать исход операции и предварительно выполняют предсказанный блок. При этом в случае ошибки много тактов тратится впустую. В процессе выполнения программы ЦП выбирает команды, которые взаимно независимы и распределяет их на параллельную обработку. Если ЦП обнаруживает оператор ветвления, он не пытается предсказать переход, а начинает выполнять все возможные ветви программы. Таким образом, могут быть обработаны все ветви программы, но без записи полученного результата. В определенный момент процессор наконец «узнает» о реальном исходе условного оператора, записывает в память результат «правильной ветви» и отменяет остальные результаты. В то же время, если компилятор не «отметил» ветвление, процессор действует как обычно — пытается предсказать путь ветвления и т. д. Испытания показали, что описанная технология позволяет устранить более половины ветвлений в типичной программе, и, следовательно, уменьшить более чем в 2 раза число возможных ошибок в предсказаниях.

Слайд 52: Динамическое исполнение (dynamic execution technology)

Опережающее чтение данных (speculative loading), т. е. загрузка данных в регистры с опережением, до того, как определилось реальное ветвление программы (переход управления). Позволяет избегать ситуации, когда процессору приходится ожидать прихода данных, чтобы начать их обработку. Прежде всего, компилятор анализирует программу, определяя команды, которые требуют приема данных из оперативной памяти. Там, где это возможно, он вставляет команды опережающего чтения и парную команду контроля опережающего чтения (speculative check). В то же время компилятор переставляет команды таким образом, чтобы ЦП мог их обрабатывать параллельно. В процессе работы ЦП встречает команду опережающего чтения и пытается выбрать данные из памяти. Может оказаться, что они еще не готовы (результат работы блока команд, который еще не выполнился). Обычный процессор в этой ситуации выдает сообщение об ошибке, однако система откладывает «сигнал тревоги» до момента прихода процесса в точку «команда проверки опережающего чтения». Если к этому моменту все предшествующие подпроцессы завершены и данные считаны, то обработка продолжается, в противном случае вырабатывается сигнал прерывания. Возможность располагать команду предварительной загрузки до ветвления очень существенна, так как позволяет загружать данные задолго до момента использования (напомним, что в среднем каждая шестая команда является командой ветвления).

Слайд 53: Динамическое исполнение (dynamic execution technology)

Многократное декодирование команд В то время как традиционный процессор линейно переводит команды в тактовые микрокоманды и последовательно их выполняет, ЦП с многократным декодированием сначала преобразует коды исходных команд программы в некоторые вторичные псевдокоды (предварительное декодирование, или предеко-дирование), которые затем более эффективно исполняет ядро процессора. Декодирование команд CISC VLIW в RISC. Указанные ранее достоинства RISC-архитектуры привели к тому, что во многих современных CISC-процессорах используется RISC-ядро, выполняющее обработку данных. При этом поступающие сложные и разноформатные команды предварительно преобразуются в последовательность простых RISC-операций, быстро выполняемых этим процессорным ядром. Таким образом, работают, например, современные модели процессоров Pentium и К7, которые по внешним показателям относятся к CISC-процессорам. Использование RISC-архитектуры является характерной чертой многих современных процессоров.

Слайд 54: Динамическое исполнение (dynamic execution technology)

Макрослияние (macrofusion). В процессорах предыдущих поколений каждая выбранная команда отдельно декодируется и выполняется. Макрослияние позволяет объединять типичные пары последовательных команд (например, сравнение, сопровождающееся условным переходом) в единственную внутреннюю команду-микрооперацию (МкОП, micro-op) в процессе декодирования. В дальнейшем две команды выполняются как одна МкОП, сокращая полный объем работы процессора. Микрослияние (micro-op fusion). В современных доминирующих процессорах команды х86 (macro-ops) обычно расчленяются на МкОП прежде, чем передаются на конвейер процессора. Микрослияние группирует и соединяет МкОП, уменьшая их число. Исследования показали, что слияние МкОП вкупе с выполнением команд в измененном порядке может уменьшить число МкОП более чем на 10 %. Данная технология использована в системах Intel Core, а ранее апробировалась в ПЦ мобильных систем Pentium M.

Слайд 55: Технологии энергосбережения

OnNow PC — способ управления энергопотреблением системы, который заключается в значительном уменьшении потребления электрической энергии, но так, чтобы система в любой момент времени была готова к работе без перезагрузки ОС. Система при включении остается способной реагировать на внешние события: нажатие кнопки пользователем, сигнал из сети. Это обеспечивается тем, что небольшая часть системы остается постоянно включенной. Технология OnNow PC требует выполнения следующих условий: операционная система берет на себя управление энергопотреблением; все устройства, входящие в систему, должны допускать возможность эффективного регулирования потребления ими электрической энергии; должен быть предусмотрен ряд определяемых операционной системой последовательных энергетических состояний, переходящих одно в другое. Интеллектуальное управление электропитанием (Intel Intelligent Power Capability) — уменьшение потребления энергии путем включения именно тех логических блоков, которые требуются в данный момент. Enhanced Intel Speed STep (EIST) — идентичен механизму, осуществленному в процессорах Intel мобильных ПК, который позволяет процессору уменьшать его тактовую частоту, когда не требуется высокая загрузка, таким образом значительно сокращая нагрев центрального процессора и потребление мощности.

Слайд 56: Технология Intel Hyper-Threading

Технология одновременной многопоточности (Simultaneous Multi-Threading - SMT), которая применяется Intel носит название Hyper-Threading. Что бы понять, как работает новая технология, необходимо дать определение понятию поток, как выполняются эти потоки. С точки зрения процессора, поток – это набор инструкций, которые необходимо выполнить. Например: Когда вы открываете документ Microsoft Word, процессору посылается определенный набор инструкций, которые он должен выполнить. Потоки могут прерывать друг друга, при этом процессор запоминает значение счетчика команд в стеке и загружает в счетчик новое значение. Но ограничение в этом процессе все равно существует – в каждую единицу времени можно выполнять лишь один поток.

Слайд 57: Технология Intel Hyper-Threading

ОДНАКО: Потоки могут прерывать друг друга ;-( Существует общеизвестный способ решения данной проблемы. Заключается он в использовании двух процессоров – если один процессор в каждый момент времени может выполнять один поток, то два процессора за ту же единицу времени могут выполнять уже два потока. Для такой работы и приложение, и операционная система должны поддерживать многопроцессорность. Способность распределить выполнение нескольких потоков по ресурсам компьютера часто называют многопоточностью. При этом и операционная система должна поддерживать многопоточность. Приложения также должны поддерживать многопоточность, чтобы максимально эффективно использовать ресурсы компьютера. Поток 1 Поток 2 CPU1 CPU2

Слайд 58: Технология Intel Hyper-Threading

Классические процессоры лишь частично задействуют свои возможности. Например: Pentium 4 процессор обладает, в общей сложности, семью исполнительными устройствами, два из которых могут работать с удвоенной скоростью – две операции (микрооперации) за такт. Но, в любом случае, нет программы, которая смогла бы заполнить инструкциями сразу все эти устройства. Обычные программы (офисные пакеты) обходятся несложными целочисленными вычислениями, да несколькими операциями загрузки и хранения данных, а операции с плавающей точкой остаются в стороне. Другие же программы главным образом загружают работой устройства для операций с плавающей точкой.

Слайд 59: Гипотетический процессор

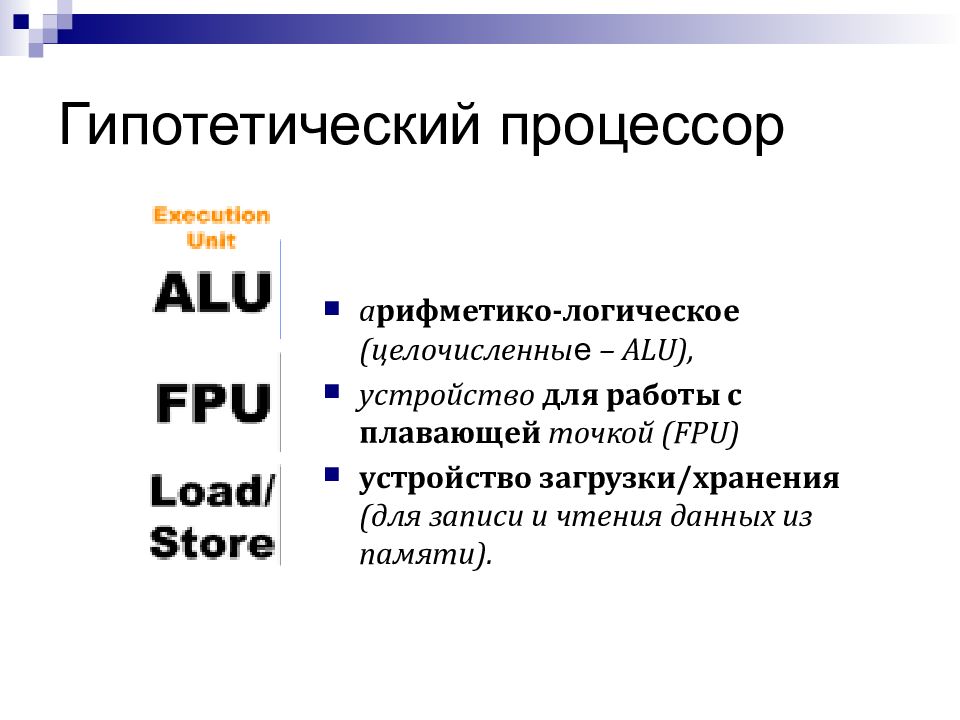

а рифметико-логическое (целочисленны е – ALU), устройство для работы с плавающей точкой (FPU) устройство загрузки/хранения (для записи и чтения данных из памяти).

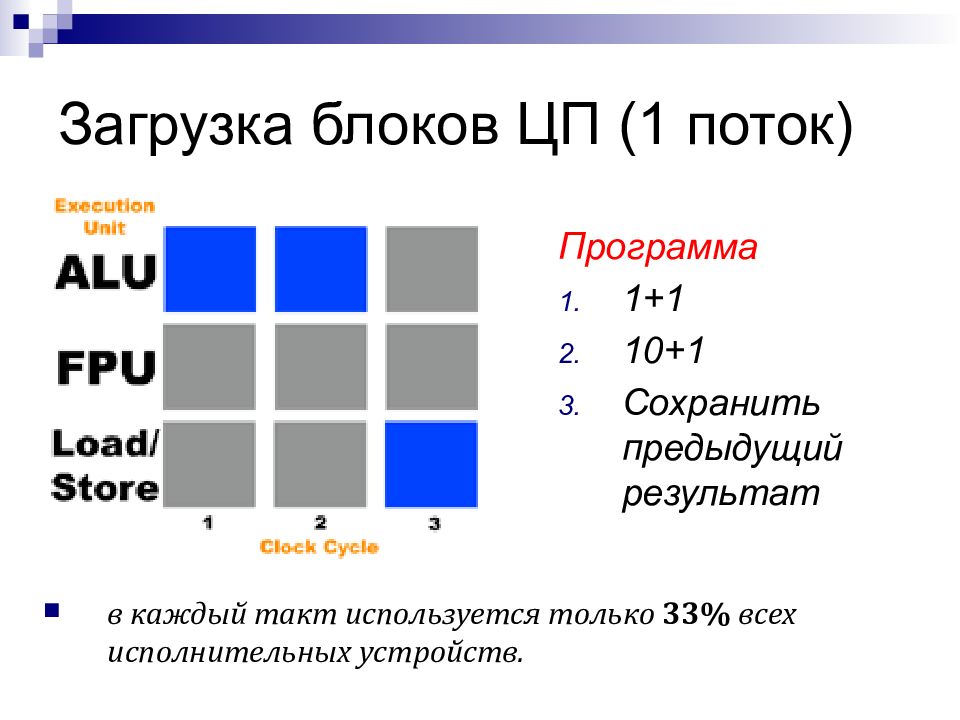

Слайд 60: Загрузка блоков ЦП (1 поток)

Программа 1+1 10+1 Сохранить предыдущий результат в каждый такт используется только 33% всех исполнительных устройств.

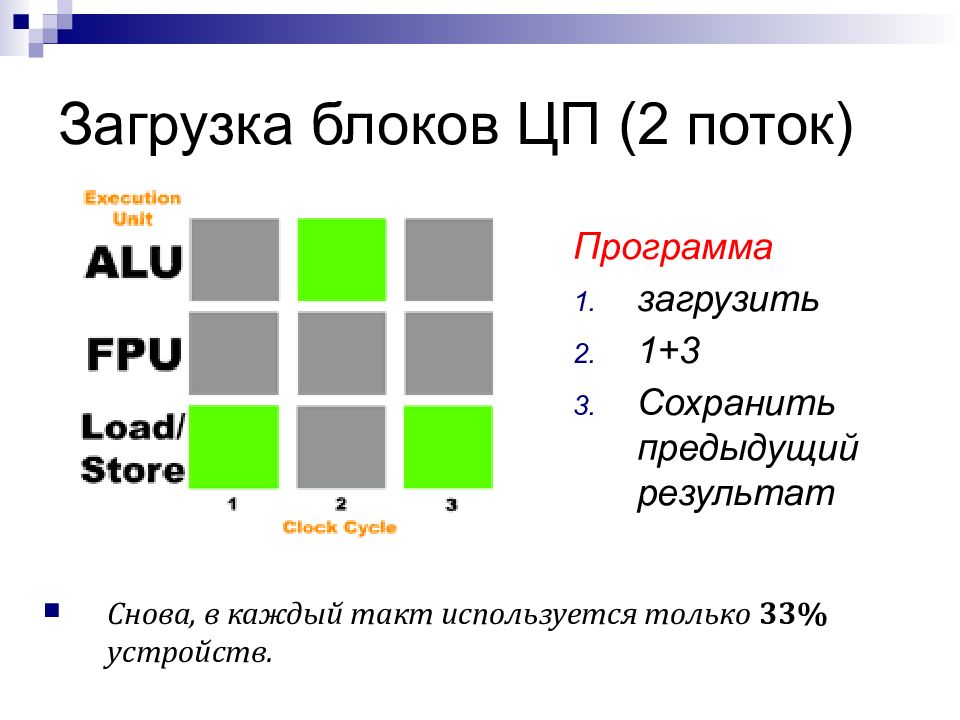

Слайд 61: Загрузка блоков ЦП (2 поток)

Программа загрузить 1+3 Сохранить предыдущий результат Снова, в каждый такт используется только 33% устройств.

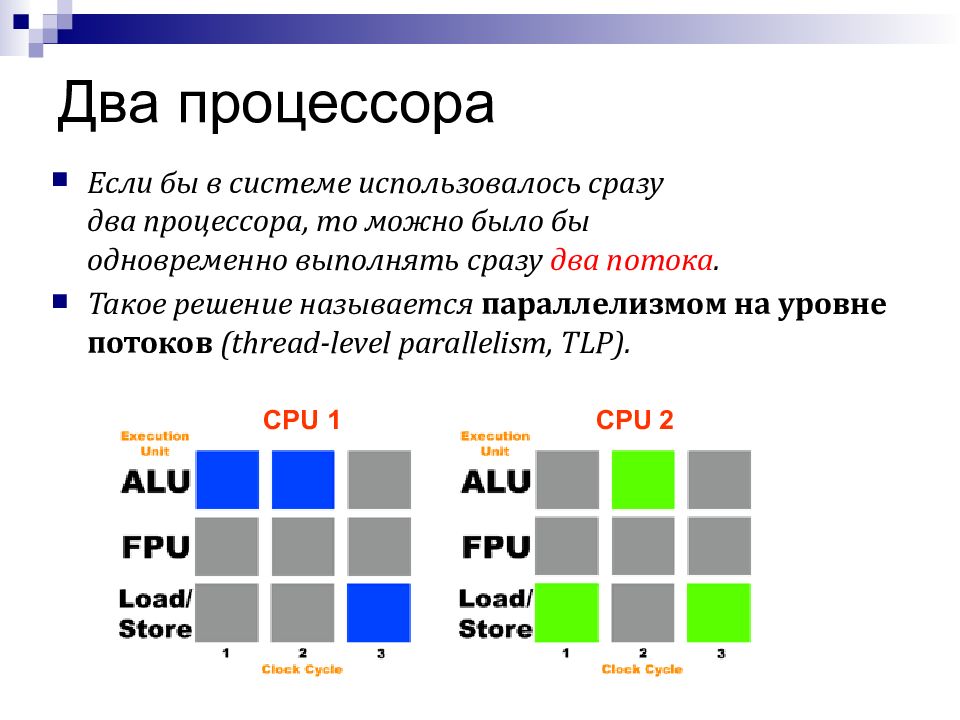

Слайд 62: Два процессора

Если бы в системе использовалось сразу два процессора, то можно было бы одновременно выполнять сразу два потока. Такое решение называется параллелизмом на уровне потоков (thread-level parallelism, TLP). CPU 1 CPU 2

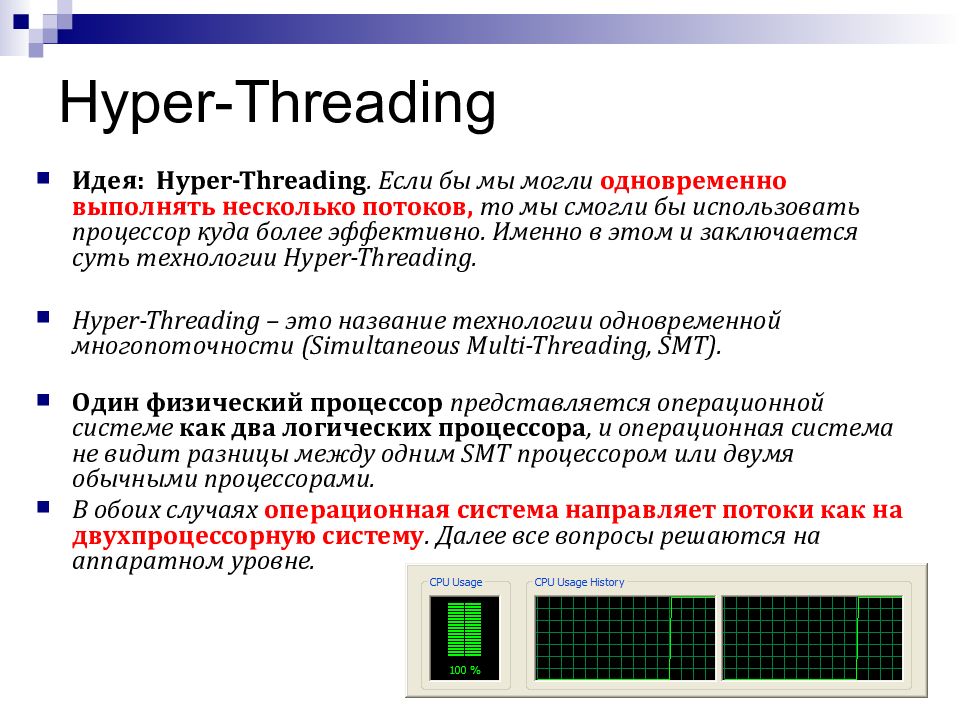

Слайд 63: Hyper-Threading

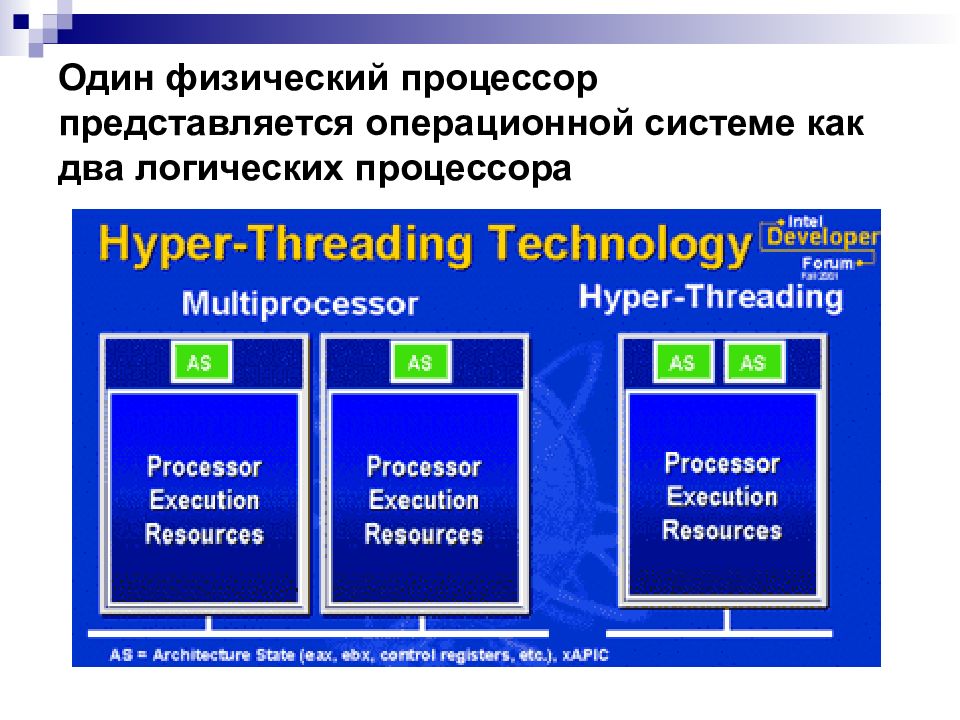

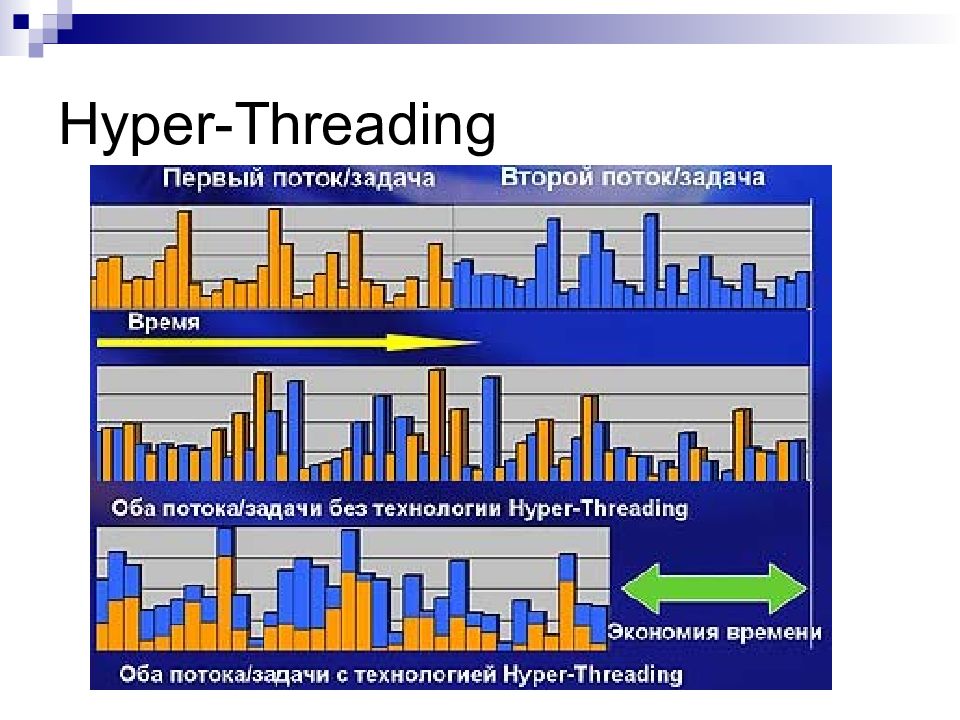

Идея: Hyper-Threading. Если бы мы могли одновременно выполнять несколько потоков, то мы смогли бы использовать процессор куда более эффективно. Именно в этом и заключается суть технологии Hyper-Threading. Hyper-Threading – это название технологии одновременной многопоточности (Simultaneous Multi-Threading, SMT). Один физический процессор представляется операционной системе как два логических процессора, и операционная система не видит разницы между одним SMT процессором или двумя обычными процессорами. В обоих случаях операционная система направляет потоки как на двухпроцессорную систему. Далее все вопросы решаются на аппаратном уровне.

Слайд 64: Один физический процессор представляется операционной системе как два логических процессора

Слайд 65: Hyper-Threading

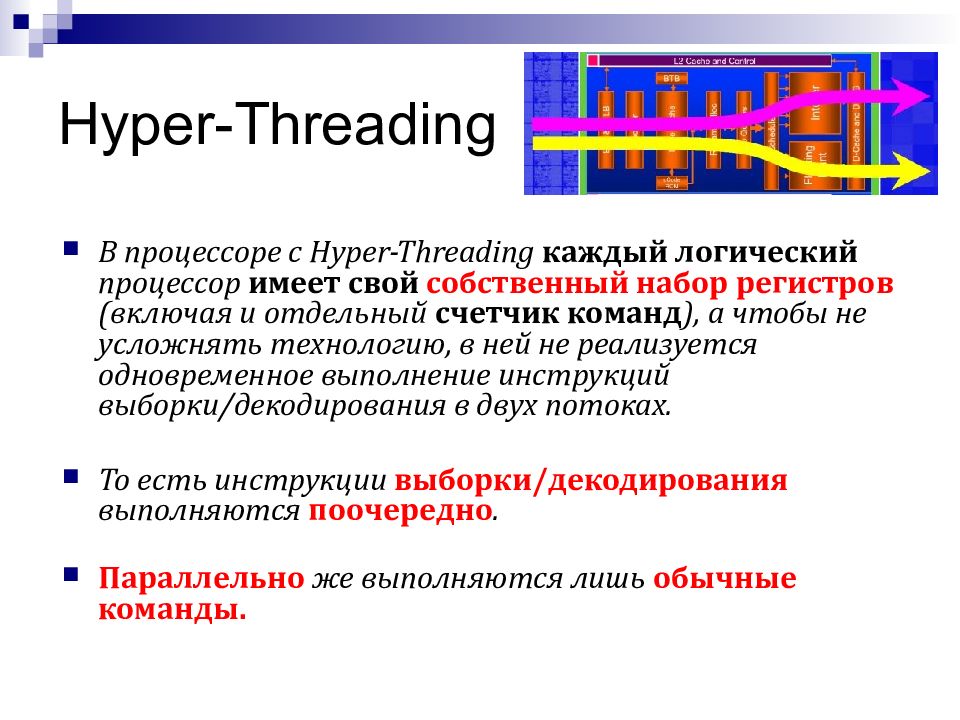

В процессоре с Hyper-Threading каждый логический процессор имеет свой собственный набор регистров (включая и отдельный счетчик команд ), а чтобы не усложнять технологию, в ней не реализуется одновременное выполнение инструкций выборки/декодирования в двух потоках. То есть инструкции выборки/декодирования выполняются поочередно. Параллельно же выполняются лишь обычные команды.

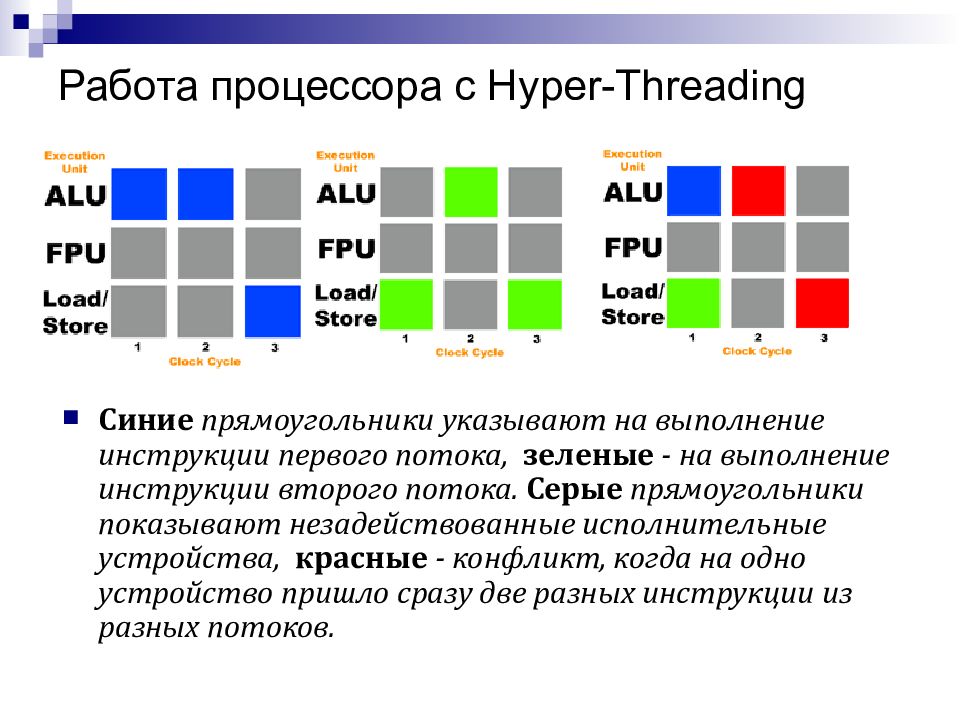

Слайд 66: Работа процессора с Hyper-Threading

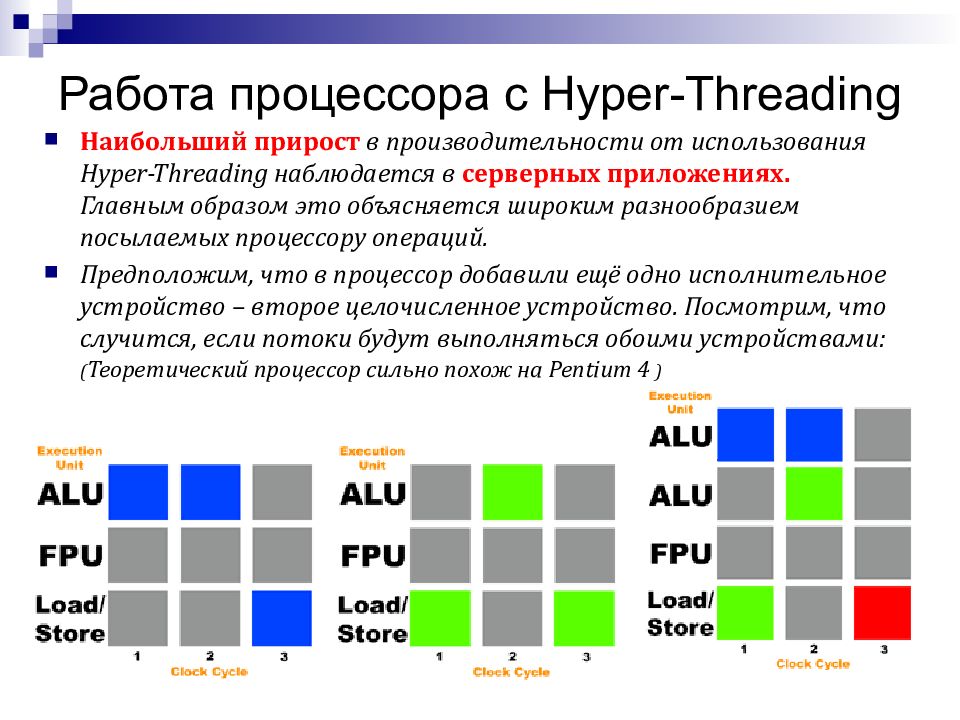

Синие прямоугольники указывают на выполнение инструкции первого потока, зеленые - на выполнение инструкции второго потока. Серые прямоугольники показывают незадействованные исполнительные устройства, красные - конфликт, когда на одно устройство пришло сразу две разных инструкции из разных потоков.

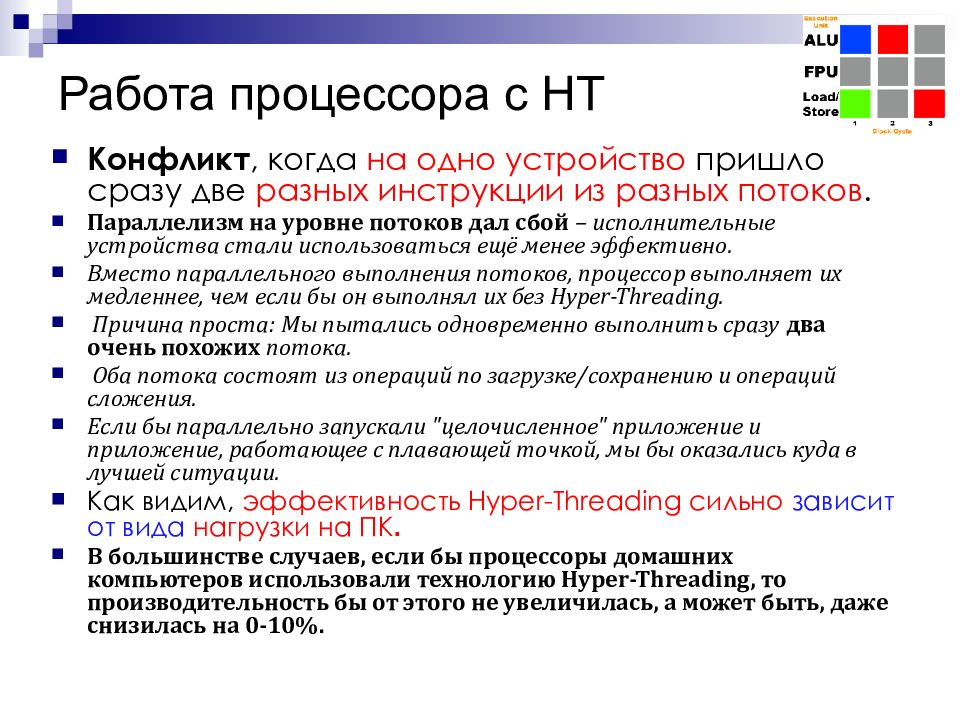

Слайд 67: Работа процессора с HT

Конфликт, когда на одно устройство пришло сразу две разных инструкции из разных потоков. Параллелизм на уровне потоков дал сбой – исполнительные устройства стали использоваться ещё менее эффективно. Вместо параллельного выполнения потоков, процессор выполняет их медленнее, чем если бы он выполнял их без Hyper-Threading. Причина проста : Мы пытались одновременно выполнить сразу два очень похожих потока. Оба потока состоят из операций по загрузке/сохранению и операций сложения. Если бы параллельно запускали "целочисленное" приложение и приложение, работающее с плавающей точкой, мы бы оказались куда в лучшей ситуации. Как видим, эффективность Hyper-Threading сильно зависит от вида нагрузки на ПК. В большинстве случаев, если бы процессоры домашних компьютеров использовали технологию Hyper-Threading, то производительность бы от этого не увеличилась, а может быть, даже снизилась на 0-10%.

Слайд 68: Работа процессора с Hyper-Threading

Наибольший прирост в производительности от использования Hyper-Threading наблюдается в серверных приложениях. Главным образом это объясняется широким разнообразием посылаемых процессору операций. Предположим, что в процессор добавили ещё одно исполнительное устройство – второе целочисленное устройство. Посмотрим, что случится, если потоки будут выполняться обоими устройствами: ( Теоретический процессор сильно похож на Pentium 4 )

Слайд 69: Оптимизация кода для HT

Было бы мало смысла просто добавлять в процессор дополнительные исполнительные устройства с целью увеличения производительности от использования Hyper-Threading. С точки зрения производства это было бы крайне дорого. Вместо этого, Intel предложила разработчикам оптимизировать программы под Hyper-Threading. Используя инструкцию HALT, можно приостановить работу одного из логических процессоров, и тем самым увеличить производительность приложений, которые не выигрывают от Hyper-Threading. Итак, приложение не станет работать медленнее, вместо этого один из логических процессоров будет остановлен, и система будет работать на одном логическом процессоре – производительность будет такой же, что и на однопроцессорных компьютерах. Затем, когда приложение сочтет, что от Hyper-Threading оно выиграет в производительности, второй логический процессор просто возобновит свою работу.

Слайд 71: Технология антивирусной защиты «невыполнимых битов» (No-eXecute bit)

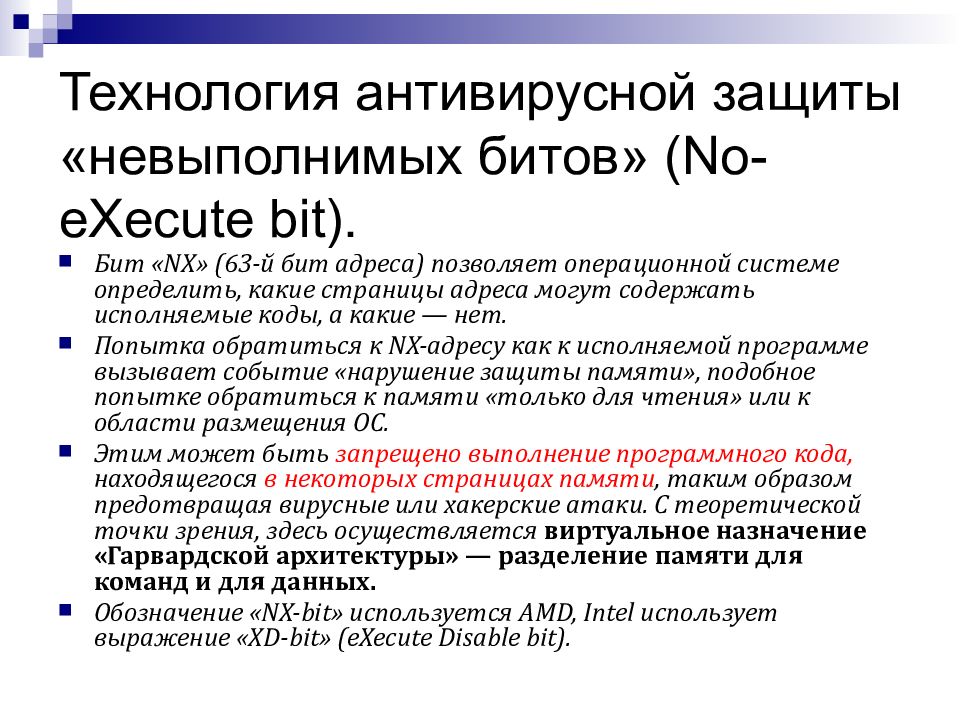

Бит «NX» (63-й бит адреса) позволяет операционной системе определить, какие страницы адреса могут содержать исполняемые коды, а какие — нет. Попытка обратиться к NX-адресу как к исполняемой программе вызывает событие «нарушение защиты памяти», подобное попытке обратиться к памяти «только для чтения» или к области размещения ОС. Этим может быть запрещено выполнение программного кода, находящегося в некоторых страницах памяти, таким образом предотвращая вирусные или хакерские атаки. С теоретической точки зрения, здесь осуществляется виртуальное назначение «Гарвардской архитектуры» — разделение памяти для команд и для данных. Обозначение «NX-bit» используется AMD, Intel использует выражение «XD-bit» (eXecute Disable bit).

Слайд 72: Расширения архитектуры x86 (x86 extended features)

Расширения архитектуры x86 (x86 extended features) — инженерные решения, присутствуют в одних моделях, и отсутствуют в других. Разработчики программного обеспечения, прежде чем использовать их в собственных программах, должны выполнить специальную команду CPUID, которая сообщает о наличии тех или иных расширений. Иногда расширения становятся часто используемыми в популярных программах, тогда их начинают включать в свои процессоры практически все производители. Наиболее известные из расширений MMX, SSE, 3DNow!, Hyper-threading. В основном, новые расширения разрабатываются фирмой Intel и, затем, подхватываются другими производителями. Но иногда бывает так, что сама Intel включает в свои процессоры расширения, созданные иными фирмами. К примеру, так было с архитектурой x86-64, впервые разработанной компанией AMD, а уже впоследствии реализованная Intel как Intel64/EM64T.

Слайд 73: Расширения MMX

MMX (Multimedia Extensions — мультимедийные расширения) — коммерческое название дополнительного набора инструкций, выполняющих характерные для процессов кодирования/декодирования потоковых аудио/видео данных действия за одну машинную инструкцию. Впервые появился в процессорах Pentium MMX. Разработан в лаборатории Intel в Хайфе, Израиль, в первой половине 1990-х. Регистры MMX. Расширение MMX включает в себя восемь 64-битных регистров общего пользования MM0—MM7. Физически никаких новых регистров с введением MMX не появилось. MM0—MM7 — это в точности мантиссы восьми регистров FPU (Математический сопроцессор), от R0—R7. Таким образом, нельзя одновременно пользоваться командами Математического сопроцессора и MMX. Типы данных MMX. Команды технологии MMX работают с 64-разрядными целочисленными данными, а также с данными, упакованными в группы (векторы) общей длиной 64 бита. В систему команд введено 57 дополнительных инструкций для одновременной обработки нескольких единиц данных.

Слайд 74: Команды SSE

SSE ( Streaming SIMD Extensions, потоковое SIMD- расширение процессора ) — это SIMD ( Single Instruction, Multiple Data, Одна инструкция — множество данных) набор инструкций, разработанный Intel и впервые представленный в процессорах серии Pentium III как ответ на аналогичный набор инструкций 3DNow! от AMD, который был представлен годом раньше. SSE включает в архитектуру процессора восемь 128-битных регистров (xmm0 до xmm7), каждый из которых трактуется как 4 последовательных значения с плавающей точкой одинарной точности. SSE включает в себя набор инструкций, который производит операции со скалярными и упакованными типами данных. Преимущество в производительности достигается в том случае, когда необходимо произвести одну и ту же последовательность действий над разными данными. Реализация блоков SIMD осуществляется распараллеливанием вычислительного процесса между данными, то есть, когда через один блок проходит поочерёдно множество потоков данных.

Слайд 75: Расширения команд SSE2

SSE2 (Streaming SIMD Extensions 2, потоковое SIMD-расширение процессора) — это SIMD (англ. Single Instruction, Multiple Data, Одна инструкция — множество данных) набор инструкций, разработанный Intel, и впервые представленный в процессорах серии Pentium 4. SSE2 использует восемь 128-битных регистров (xmm0 до xmm7), включённых в архитектуру x86 с вводом расширения SSE, каждый из которых трактуется как 2 последовательных значения с плавающей точкой двойной точности. SSE2 включает в себя набор инструкций, который производит операции со скалярными и упакованными типами данных. Также SSE2 содержит инструкции для потоковой обработки целочисленных данных в тех же 128-битных xmm регистрах, что делает это расширение более предпочтительным для целочисленных вычислений, нежели использование набора инструкций MMX, появившегося гораздо раньше. Преимущество в производительности достигается в том случае, когда необходимо произвести одну и ту же последовательность действий над большим набором однотипных данных.

Слайд 76: Расширения команд SSE3

SSE3 (PNI — Prescott New Instruction) — третья версия SIMD-расширения Intel, потомок SSE, SSE2 и MMX. Впервые представлено 2 февраля 2004 года в ядре Prescott процессора Pentium 4. В 2005 AMD предложила свою реализацию SSE3 для процессоров Athlon 64 (ядра Venice, San Diego и Newark). Набор SSE3 содержит 13 инструкций: FISTTP (x87), MOVSLDUP (SSE), MOVSHDUP (SSE), MOVDDUP (SSE2), LDDQU (SSE/SSE2), ADDSUBPD (SSE), ADDSUBPD (SSE2), HADDPS (SSE), HSUBPS (SSE), HADDPD (SSE2), HSUBPD (SSE2), MONITOR (нет аналога в SSE3 для AMD), MWAIT (нет аналога в SSE3 для AMD).

Слайд 77: Расширения команд SSSE3

Supplemental Streaming SIMD Extension 3 (SSSE3) — это обозначение данное Intel’ом четвёртому расширению системы команд. Предыдущее имело обозначение SSE3 и Intel добавил ещё один символ 'S' вместо того, чтобы увеличить номер расширения, возможно потому, что они посчитали SSSE3 простым дополнением к SSE3. Часто, до того как стало использоваться официальное обозначение SSSE3, эти новые команды назывались SSE4. Также их называли кодовыми именами Tejas New Instructions (TNI) и Merom New Instructions (MNI) по названию процессоров, где впервые Intel намеревалась поддержать эти новые команды. Появившись в Intel Core Microarchitecture, SSSE3 доступно в сериях процессоров Xeon 5100 (Server и Workstation версии), а также в процессорах Intel Core 2 (Notebook и Desktop версии) и Intel Atom. Новыми в SSSE3, по сравнению с SSE3, являются 16 уникальных команд, работающих с упакованными целыми. Каждая из них может работать как с 64-х битными (MMX), так и с 128-ми битными (XMM) регистрами, поэтому Intel в своих материалах ссылается на 32 новые команды. Процессоры поддерживающие SSSE3: Xeon 5100 Series, Intel Core 2,Intel Celeron (ядро Conroe-L), Intel Atom.

Слайд 78: Расширения команд SSE4

SSE4 - новый набор команд микроархитектуры Intel Core, впервые реализованный в процессорах серии Penryn (не следует путать с SSE4A от AMD). SSE4 состоит из 54 инструкций, 47 из них относят к SSE4.1 (они есть в процессорах Penryn). Полный набор команд (SSE4.1 и SSE4.2, то есть 47 + оставшиеся 7 команд) доступен только в процессорах Intel с микроархитектурой Nehalem, которые были выпущены в середине ноября 2008 года. Ни одна из SSE4 инструкций не работает с 64-х битными mmx регистрами (только с 128-ми битными xmm0-15). Компилятор языка С++ от Intel начиная с версии 10 генерирует инструкции SSE4 при задании опции -QxS. Добавлены инструкции, ускоряющие компенсацию движения в видеокодеках, быстрое чтение из USWC памяти, множество инструкций для упрощения векторизации программ компиляторами. Кроме того, в SSE4.2 добавлены инструкции обработки строк 8/16 битных символов, вычисления CRC32, popcnt.

Слайд 79: Расширения команд 3Dnow!

3DNow! — дополнительное расширение MMX для процессоров AMD, начиная с AMD K6 3D. Причиной создания 3DNow! послужило стремление завоевать превосходство над процессорами производства компании Intel в области обработки мультимедийных данных. Хотя это расширение является разработкой AMD, его также интегрировали в свои процессоры IBM, Cyrix и другие. Технология 3DNow! ввела 21 новую команду процессора и возможность оперировать 32-битными вещественными типами в стандартных MMX-регистрах. Также были добавлены специальные инструкции, оптимизирующие переключение в режим MMX/3DNow! (femms, которая заменяла стандартную инструкцию emms) и работу с кэшем процессора. Таким образом технология 3DNow! расширяла возможности технологии MMX, не требуя введения новых режимов работы процессора и новых регистров. Перед началом работы с расширением 3DNow! следует убедиться, что ЦП их поддерживает.

Слайд 80: Будущие расширения команд

Расширение системы команд AES ( Advanced Encryption Standard) — расширение системы команд x86 для микропроцессоров, предложенное компанией Intel в марте 2008. Целью данного расширения является ускорение приложений, использующий шифрование и дешифрование по алгоритму AES. Сходное расширение PadLock engine существует в микропроцессорах от VIA Technologies. Микропроцессоры с расширением команд AES: Intel Проектируемый Intel Westmere (Nehalem на 32нм техпроцессе), 4й квартал 2009. AMD: Проектируемый Bulldozer, 2011.

Слайд 81: Процессоры в «железе»

Современные ЦП, выполняются в виде отдельных микросхем (чипов), реализующих все особенности, присущие данного рода устройствам, называют микропроцессорами. С середины 1980-х последние практически вытеснили прочие виды ЦП, вследствие чего термин стал всё чаще и чаще восприниматься как обыкновенный синоним слова «микропроцессор». Тем не менее, это не так: центральные процессорные устройства некоторых суперкомпьютеров даже сегодня представляют собой сложные комплексы больших (БИС) и сверхбольших интегральных схем (СБИС).

Слайд 82: Многоядерные процессоры

Содержат несколько процессорных ядер в одном корпусе (на одном или нескольких кристаллах). Процессоры, предназначенные для работы одной копии операционной системы на нескольких ядрах, представляют собой высокоинтегрированную реализацию мультипроцессорности. Двухъядерность процессоров включает такие понятия, как наличие логических и физических ядер: например двухъядерный процессор Intel Core Duo состоит из одного физического ядра, которое в свою очередь разделено на два логических. Процессор Intel Core 2 Quad состоит из четырёх физических ядер, что существенно влияет на скорость его работы.

Слайд 83: Многоядерные процессоры

10 сентября 2007 года были выпущены в продажу нативные (в виде одного кристалла) четырёхъядерные процессоры для серверов AMD Opteron, имевшие в процессе разработки кодовое название AMD Opteron Barcelona. 19 ноября 2007 года вышел в продажу четырёхъядерный процессор для домашних компьютеров AMD Phenom. Эти процессоры реализуют новую микроархитектуру K8L (K10). 27 сентября 2006 года Intel продемонстрировала прототип 8-ядерного процессора. Предполагается, что массовое производство подобных процессоров станет возможно не раньше перехода на 32-нанометровый техпроцесс, а это в свою очередь ожидается к 2010 году.

Слайд 84: Многоядерные процессоры

26 октября 2009 года Tilera анонсировала 10-ядерный процессор широкого назначения серии TILE-Gx. Каждое процессорное ядро представляет собой отдельный процессор с кэшем 1, 2 и 3 уровней. Ядра, память и системная шина связаны посредством технологии Mesh Network. Процессоры производятся по 40-нм нормам техпроцесса и работают на тактовой частоте 1,5 ГГц. Выпуск 10-ядерных процессоров назначен на начало 2011 года. На данный момент массово доступны двух-, четырёх- и шестиядерные процессоры, в частности Intel Core 2 Duo на 65-нм ядре Conroe (позднее на 45-нм ядре Wolfdale) и Athlon 64 X2 на базе микроархитектуры K8. В ноябре 2006 года вышел первый четырёхъядерный процессор Intel Core 2 Quad на ядре Kentsfield, представляющий собой сборку из двух кристаллов Conroe в одном корпусе. Потомком этого процессора стал Intel Core 2 Quad на ядре Yorkfield (45 нм), архитектурно схожем с Kentsfield но имеющем больший объём кэша и рабочие частоты.

Слайд 85: Многоядерные процессоры

Компания AMD пошла по собственному пути, изготовляя четырёхъядерные процессоры единым кристаллом (в отличие от Intel, первые четырехъядерные процессоры которой представляют собой фактически склейку двух двухъядерных кристаллов). Несмотря на всю прогрессивность подобного подхода первый «четырёхъядерник» фирмы, получивший название AMD Phenom X4, получился не слишком удачным. Его отставание от современных ему процессоров конкурента составляло от 5 до 30 и более процентов в зависимости от модели и конкретных задач. К 1-2 кварталу 2009 года обе компании обновили свои линейки четырёхъядерных процессоров. Intel представила семейство Core i7, состоящее из трёх моделей, работающих на разных частотах. Основными изюминками данного процессора является использование трёхканального контроллера памяти (типа DDR-3) и технологии эмулирования восьми ядер (полезно для некоторых специфических задач).

Слайд 86: Многоядерные процессоры

Кроме того, благодаря общей оптимизации архитектуры удалось значительно повысить производительность процессора во многих типах задач. Слабой стороной платформы, использующей Core i7, является её чрезмерная стоимость, так как для установки данного процессора необходима дорогая материнская плата на чипсете Intel X58 и трёхканальный набор памяти типа DDR3, также имеющий на данный момент высокую стоимость. Компания AMD в свою очередь представила линейку процессоров Phenom II X4. При её разработке компания учла свои ошибки: был увеличен объём кэша (явно недостаточный у первого «Фенома»), а производство процессора было переведено на 45 нм техпроцесс, позволивший снизить тепловыделение и значительно повысить рабочие частоты. В целом, AMD Phenom II X4 по производительности стоит вровень с процессорами Intel предыдущего поколения (ядро Yorkfield) и весьма значительно отстаёт от Intel Core i7.

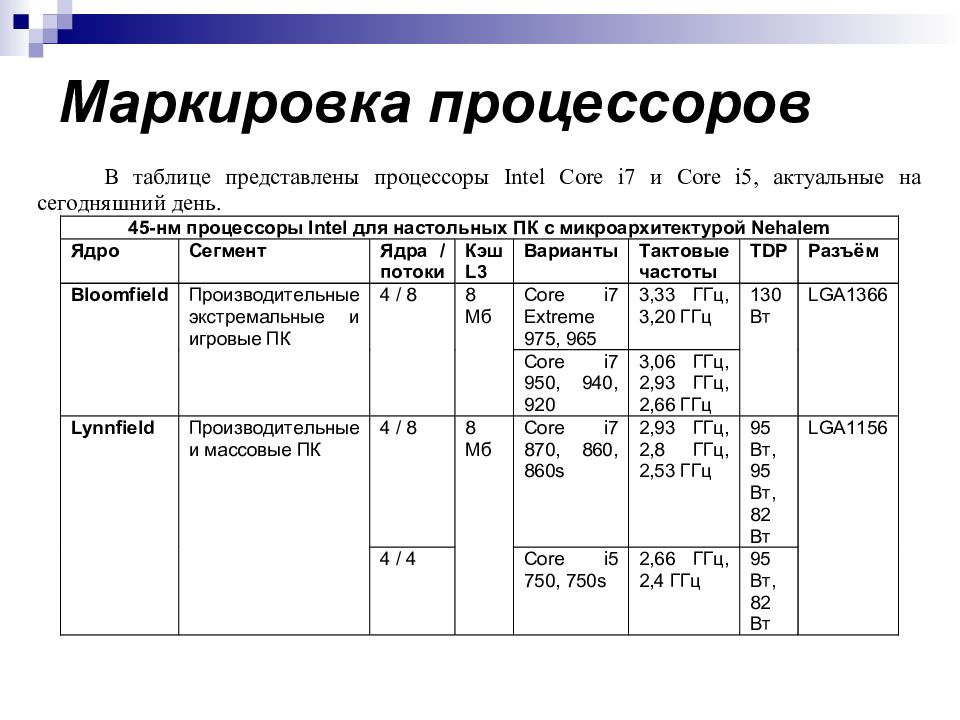

Слайд 87: Маркировка процессоров

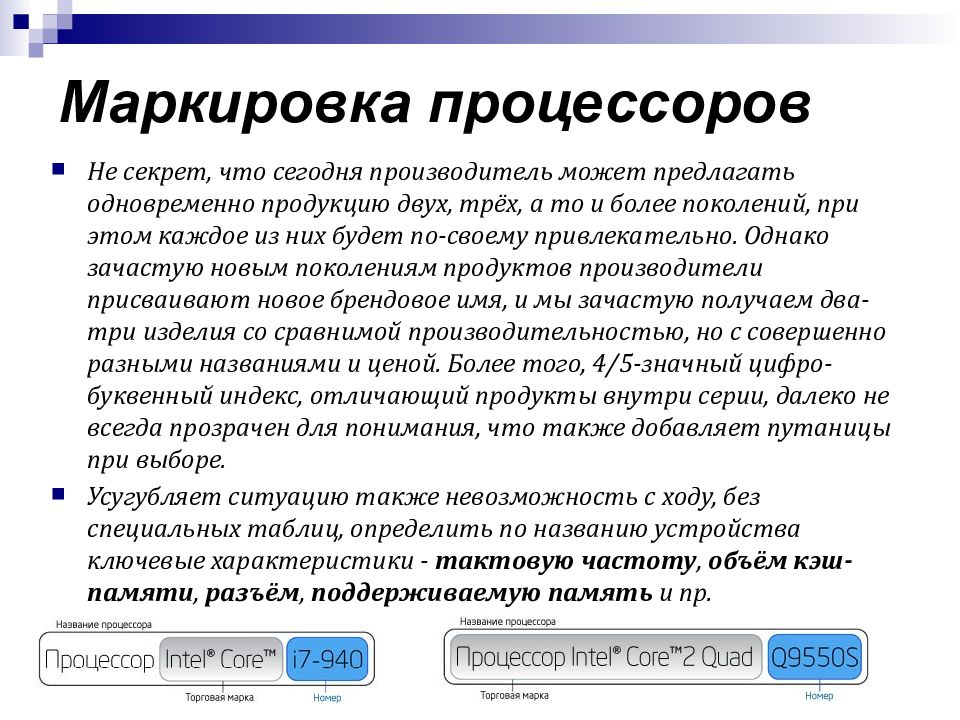

Не секрет, что сегодня производитель может предлагать одновременно продукцию двух, трёх, а то и более поколений, при этом каждое из них будет по-своему привлекательно. Однако зачастую новым поколениям продуктов производители присваивают новое брендовое имя, и мы зачастую получаем два-три изделия со сравнимой производительностью, но с совершенно разными названиями и ценой. Более того, 4/5-значный цифро-буквенный индекс, отличающий продукты внутри серии, далеко не всегда прозрачен для понимания, что также добавляет путаницы при выборе. Усугубляет ситуацию также невозможность с ходу, без специальных таблиц, определить по названию устройства ключевые характеристики - тактовую частоту, объём кэш-памяти, разъём, поддерживаемую память и пр.

Слайд 89: Маркировка процессоров

4004 : первый процессор, реализованный в одной микросхеме 71г

Слайд 90: Маркировка процессоров

16-битные процессоры: Происхождение x86 8086 8 июня 1978 года Частоты: 5 МГц с производительностью 0,33 MIPS 8 МГц с производительностью 0,66 MIPS 10 МГц с производительностью 0,75 MIPS Ширина шины: 16 бит — данные, 20 бит — адреса Количество транзисторов: 29,000 Технология: 3 мкм Адресуемая память: 1 Мбайт 10-кратная производительность 8080 Использовался в портативных вычислениях Ассемблер совместим с 8080 Использовались сегментные регистры для доступа к более, чем 64K данных одновременно, создававшие проблемы для программистов в течение многих лет.

Слайд 91: Маркировка процессоров

32-битные процессоры: Линия 80386 80386DX 17 октября 1985 Частоты: 16 МГц с производительностью от 5 до 6 MIPS 16 февраля 1987 20 МГц с производительностью от 6 до 7 MIPS 4 апреля 1988 25 МГц с производительностью 8,5 MIPS 10 апреля 1989 33 МГц с производительностью 11,4 MIPS (9.4 SPECint92 на Compaq/i 16K L2) Ширина шины: 32 бит Количество транзисторов: 275,000 Технология: 1 мкм Адресуемая память: 4 Гбайта Виртуальная память: 64 Тбайта Первый чип x86 для поддержки 32-битных наборов данных Переработанная и расширенная поддержка защиты памяти включающая страничную виртуальную память и режим виртуального 86, особенности, требующиеся для Windows 95, OS/2 Warp и Unix Использовался в вычислениях на десктопе Может адресовать достаточно памяти для управления восьмистраничной историей каждого человека на Земле Может просмотреть всю Encyclopedia Britannica за 12.5 секунд

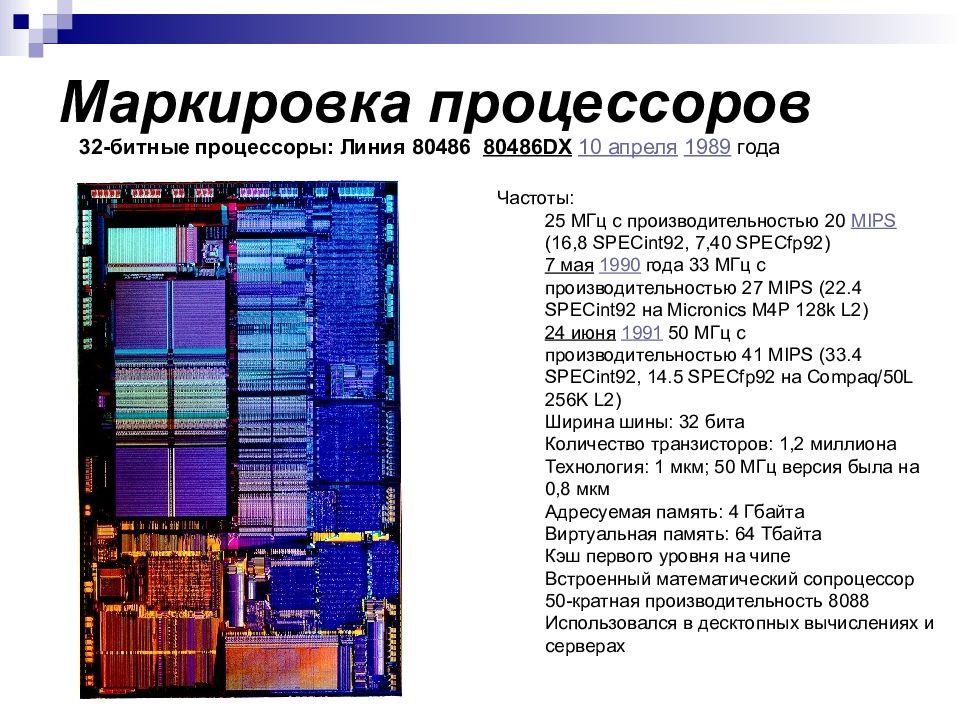

Слайд 92: Маркировка процессоров

32-битные процессоры: Линия 80486 80486DX 10 апреля 1989 года Частоты: 25 МГц с производительностью 20 MIPS (16,8 SPECint92, 7,40 SPECfp92) 7 мая 1990 года 33 МГц с производительностью 27 MIPS (22.4 SPECint92 на Micronics M4P 128k L2) 24 июня 1991 50 МГц с производительностью 41 MIPS (33.4 SPECint92, 14.5 SPECfp92 на Compaq/50L 256K L2) Ширина шины: 32 бита Количество транзисторов: 1,2 миллиона Технология: 1 мкм; 50 МГц версия была на 0,8 мкм Адресуемая память: 4 Гбайта Виртуальная память: 64 Тбайта Кэш первого уровня на чипе Встроенный математический сопроцессор 50-кратная производительность 8088 Использовался в десктопных вычислениях и серверах

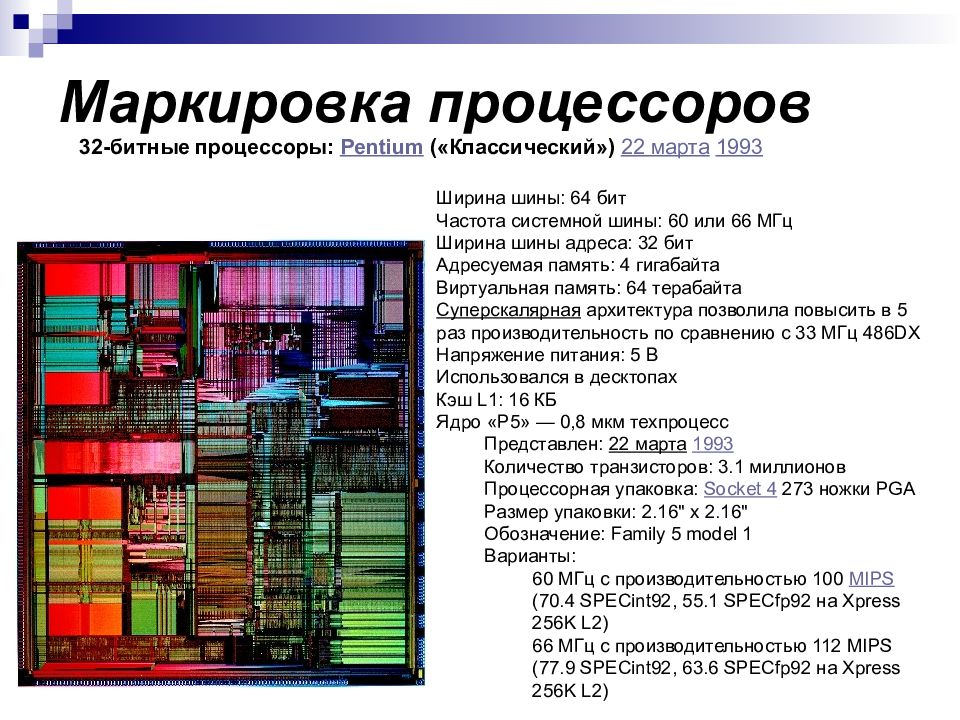

Слайд 93: Маркировка процессоров

32-битные процессоры: Pentium («Классический») 22 марта 1993 Ширина шины: 64 бит Частота системной шины: 60 или 66 МГц Ширина шины адреса: 32 бит Адресуемая память: 4 гигабайта Виртуальная память: 64 терабайта Суперскалярная архитектура позволила повысить в 5 раз производительность по сравнению с 33 МГц 486DX Напряжение питания: 5 В Использовался в десктопах Кэш L1: 16 КБ Ядро «P5» — 0,8 мкм техпроцесс Представлен: 22 марта 1993 Количество транзисторов: 3.1 миллионов Процессорная упаковка: Socket 4 273 ножки PGA Размер упаковки: 2.16" x 2.16" Обозначение: Family 5 model 1 Варианты: 60 МГц с производительностью 100 MIPS (70.4 SPECint92, 55.1 SPECfp92 на Xpress 256K L2) 66 МГц с производительностью 112 MIPS (77.9 SPECint92, 63.6 SPECfp92 на Xpress 256K L2)

Слайд 95: Маркировка процессоров

Pentium II 7 мая 1997 Pentium Pro с MMX и улучшенной производительностью для 16-битных приложений Упаковка процессора: 242-ножечный Slot 1 SEC Количество транзисторов: 7,5 миллионов Частота системной шины: 66 МГц Кэш L1: 32 КБ Внешний кэш L2: 512 КБ на 1/2 скорости Варианты: 233 МГц, представлен 7 мая 1997 года 266 МГц, представлен 7 мая 1997 года 300 МГц, представлен 7 мая 1997 года Deschutes — технологический процесс: 0,25 мкм (333, 350, 400, 450 МГц) Представлен: 26 января 1998 года Частота системной шины: 66 МГц ( вариант 333 МГц ), 100 МГц для всех моделей после Варианты: 333 МГц, представлен 26 января 1998 года 350 МГц, представлен 15 апреля 1998 года 400 МГц, представлен 15 апреля 1998 года 450 МГц, представлен 24 апреля 1998 года 233 МГц (Mobile), представлен 2 апреля 1998 года

Слайд 96: Маркировка процессоров

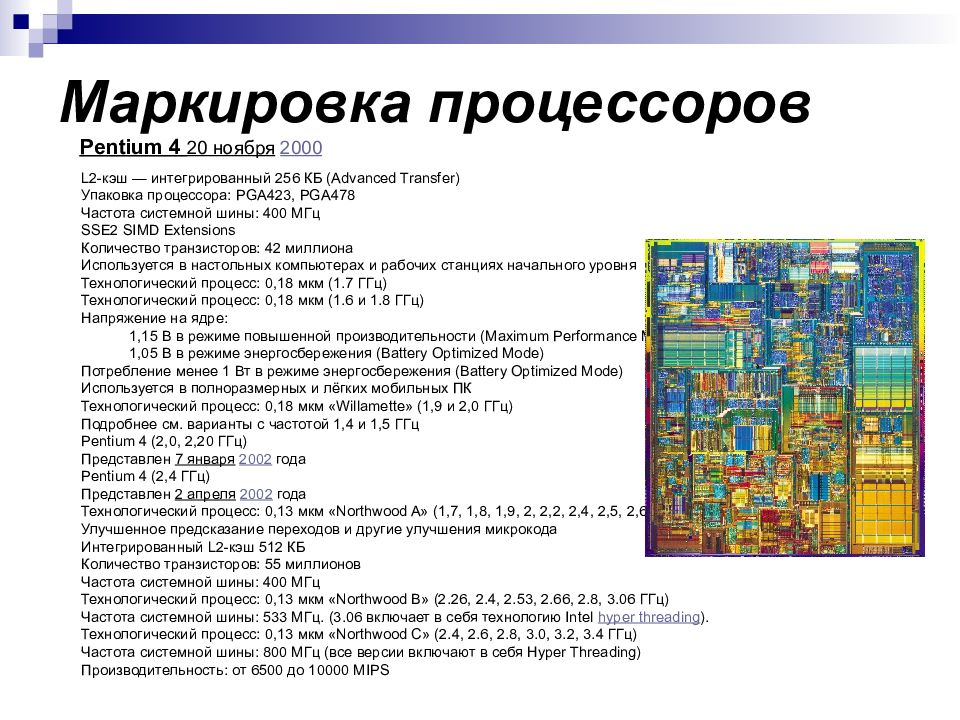

Pentium 4 20 ноября 2000 L2- кэш — интегрированный 256 КБ (Advanced Transfer) Упаковка процессора: PGA423, PGA478 Частота системной шины: 400 МГц SSE2 SIMD Extensions Количество транзисторов: 42 миллиона Используется в настольных компьютерах и рабочих станциях начального уровня Технологический процесс: 0,18 мкм (1.7 ГГц) Технологический процесс: 0,18 мкм (1.6 и 1.8 ГГц) Напряжение на ядре: 1,15 В в режиме повышенной производительности (Maximum Performance Mode); 1,05 В в режиме энергосбережения (Battery Optimized Mode) Потребление менее 1 Вт в режиме энергосбережения (Battery Optimized Mode) Используется в полноразмерных и лёгких мобильных ПК Технологический процесс: 0,18 мкм «Willamette» (1,9 и 2,0 ГГц) Подробнее см. варианты с частотой 1,4 и 1,5 ГГц Pentium 4 (2,0, 2,20 ГГц) Представлен 7 января 2002 года Pentium 4 (2,4 ГГц) Представлен 2 апреля 2002 года Технологический процесс: 0,13 мкм «Northwood A» (1,7, 1,8, 1,9, 2, 2,2, 2,4, 2,5, 2,6 ГГц) Улучшенное предсказание переходов и другие улучшения микрокода Интегрированный L2-кэш 512 КБ Количество транзисторов: 55 миллионов Частота системной шины: 400 МГц Технологический процесс: 0,13 мкм «Northwood B» (2.26, 2.4, 2.53, 2.66, 2.8, 3.06 ГГц) Частота системной шины: 533 МГц. (3.06 включает в себя технологию Intel hyper threading ). Технологический процесс: 0,13 мкм «Northwood C» (2.4, 2.6, 2.8, 3.0, 3.2, 3.4 ГГц) Частота системной шины: 800 МГц (все версии включают в себя Hyper Threading) Производительность: от 6500 до 10000 MIPS

Слайд 97: Маркировка процессоров

64-битные процессоры Xeon 26 июня 2006 Intel Core 2 27 июля 2006 Pentium Dual Core 27 июля 2006 Celeron Dual Core 20 января 2008 Intel Atom 2 апреля, 2008 Intel Core i7 16 ноября 2008

Слайд 98: Маркировка процессоров

64-битные процессоры Intel Core январе 2006 Технологический процесс: 0,065 мкм = 65 нм ( Yonah ) Представлен: в январе 2006 года Частота системной шины: 667 МГц Удвоенное (или одиночное в случае Solo) ядро с разделяемым кэшем L2 размером 2 МБ SSE3 SIMD-инструкции Варианты: Intel Core Duo T2700 2,33 ГГц Intel Core Duo T2600 2,16 ГГц Intel Core Duo T2500 2,00 ГГц Intel Core Duo T2400 1,83 ГГц Intel Core Duo T2300 1,66 ГГц Intel Core Solo T1300 1,66 ГГц Intel Core Solo T1200 1,50 ГГц 1

Слайд 99: Конструктивный фактор. Разъемы ЦП

На заре развития процессоростроения никаких особенных проблем с выбором конструкции процессора не существовало, поскольку чипы в большинстве случаев попросту запаивали в плату – как это делается сегодня с процессорами для телефонов, коммуникаторов, ряда моделей нетбуков и даже ноутбуков. Позже, благодаря возможности замены процессора, было реализовано преимущество более экономного наращивания производительной мощи без замены всей системы.

Слайд 100: Конструктивный фактор. Разъемы ЦП

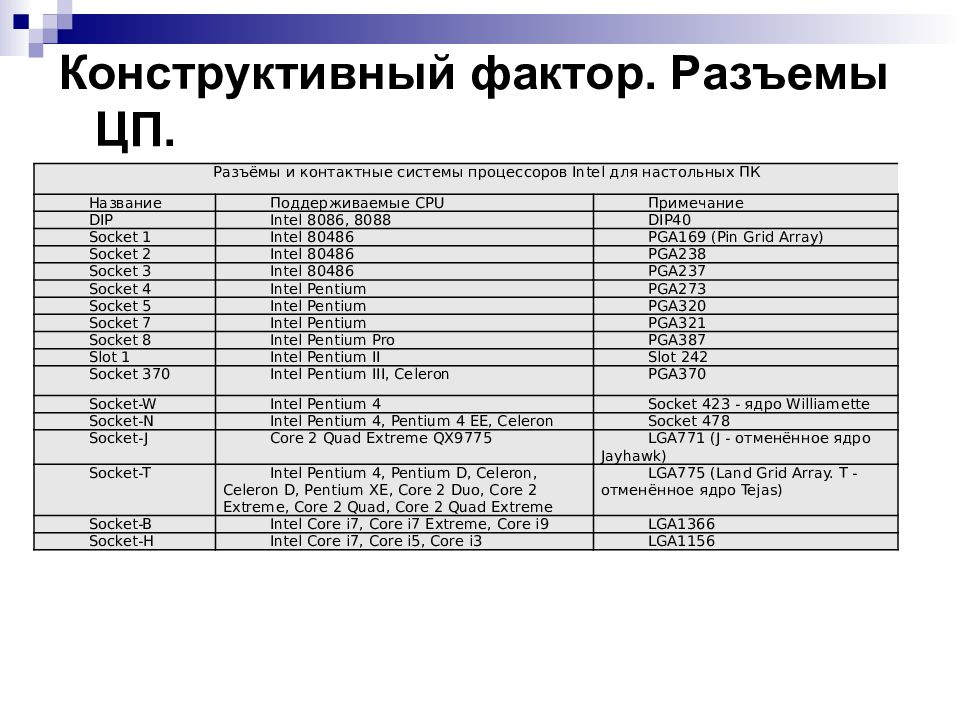

Разъёмы и контактные системы процессоров Intel для настольных ПК Название Поддерживаемые CPU Примечание DIP Intel 8086, 8088 DIP40 Socket 1 Intel 80486 PGA169 (Pin Grid Array) Socket 2 Intel 80486 PGA238 Socket 3 Intel 80486 PGA237 Socket 4 Intel Pentium PGA273 Socket 5 Intel Pentium PGA320 Socket 7 Intel Pentium PGA321 Socket 8 Intel Pentium Pro PGA387 Slot 1 Intel Pentium II Slot 242 Socket 370 Intel Pentium III, Celeron PGA370 Socket-W Intel Pentium 4 Socket 423 - ядро Williamette Socket-N Intel Pentium 4, Pentium 4 EE, Celeron Socket 478 Socket -J Core 2 Quad Extreme QX9775 LGA771 (J - отменённое ядро Jayhawk) Socket-T Intel Pentium 4, Pentium D, Celeron, Celeron D, Pentium XE, Core 2 Duo, Core 2 Extreme, Core 2 Quad, Core 2 Quad Extreme LGA775 (Land Grid Array. T - отменённое ядро Tejas) Socket-B Intel Core i7, Core i7 Extreme, Core i9 LGA1366 Socket-H Intel Core i7, Core i5, Core i3 LGA1156

Слайд 101: Пример: Микроархитектура процессора Intel Pentium 4

Конечно, новым этот процессор назвать нельзя. Время его рождения — август 2000 года. Но, пожалуй, именно 2002-й можно считать годом его окончательной победы и завоевания всеобщего признания как самим процессором, так и новой процессорной микроархитектурой. Начав со скромной (по сегодняшним меркам) тактовой частоты в 1,4 ГГц в 2000 году, сегодня Intel Pentium 4 перешагнул рубеж в 3 ГГц, но наряду с количественным ростом тактовой частоты изменение претерпела и микроархитектура процессора — к концу 2002 года корпорация Intel анонсировала процессор с поддержкой революционной технологии Hyper-Threading.

Слайд 102: Ядра P4

Современный модельный ряд процессоров Intel Pentium 4 весьма широк и включает модели, различающиеся как тактовой частотой, так и размером кэша L2, частотой процессорной шины, технологией производства, ядром процессора. Процессор Intel Pentium 4 может быть построен на ядре Willamette, Northwood или на ядре Prescott. Разница между этими двумя типами процессоров следующая: 1) Процессоры на ядре Willamette изготавливаются по 0,18-микронной технологии и имеют кэш-память второго уровня (L2), равную 256 Кбайт. 2) Процессоры на ядре Northwood изготавливаются по 0,13-микронной технологии и имеют в два раза большую кэш-память второго уровня, то есть 512 Кбайт. 3) Процессоры на ядре Prescott изготавливаются по 0,13-микронной технологии и имеют в два раза большую кэш-память второго уровня, то есть 1024 Кбайт

Слайд 103: Шина, архитектура NetBurst

У процессоров Intel Pentium 4 бывает либо 400-мегагерцевая, 533-мегагерцевая или 800- мегагерцевая процессорная шина. Разрядность этих шин одинаковая, и различаются они только своей максимальной пропускной способностью. В случае 533-мегагерцевой шины она составляет 4,2 Гбайт/с, а у 400-мегагерцевой — 3,2 Гбайт/с. Процессоры Intel Celeron аналогичны Intel Pentium 4, но отличаются вдвое меньшим размером кэша второго уровня (128 Кбайт). Кроме того, все процессоры Intel Celeron рассчитаны на 400-мегагерцевую шину. Все процессоры Intel Pentium 4 и Intel Celeron, независимо от размера кэша и ядра, объединяет одно: микроархитектура Intel NetBurst.

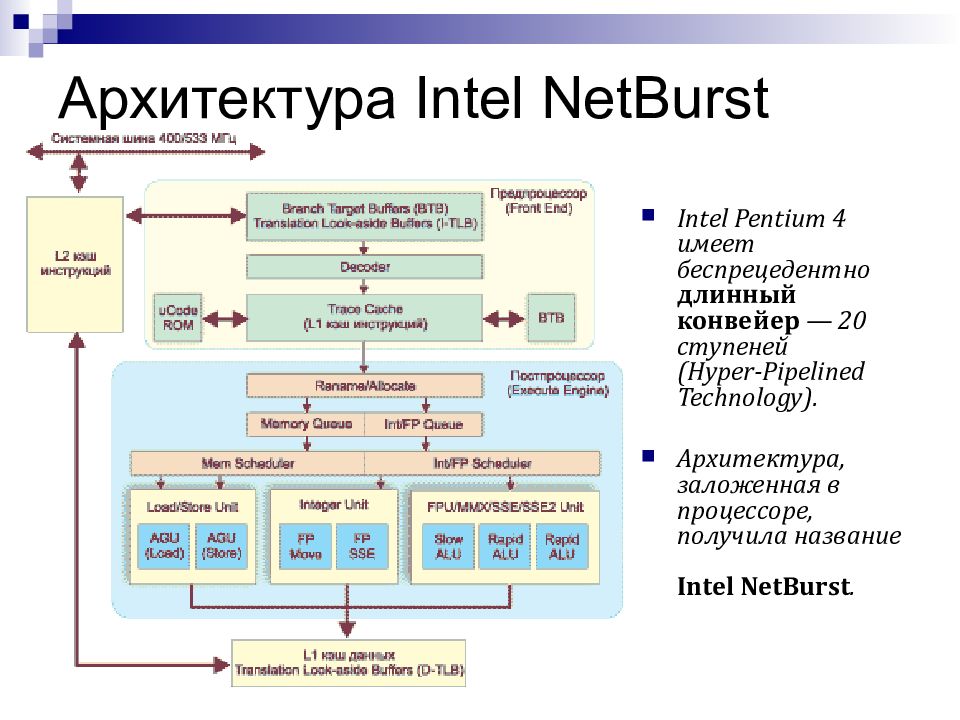

Слайд 104: Архитектура Intel NetBurst

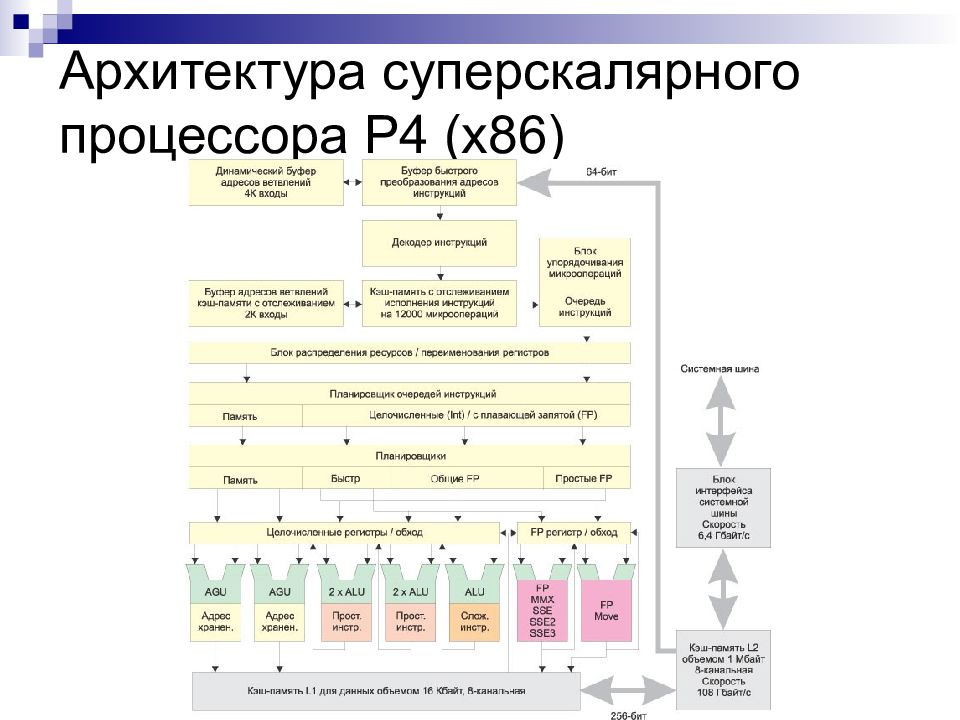

Intel Pentium 4 имеет беспрецедентно длинный конвейер — 20 ступеней (Hyper-Pipelined Technology). Архитектура, заложенная в процессоре, получила название Intel NetBurst.

Слайд 105: Ключевые особенности P4

400/533/800-мегагерцевая системная шина; Конвейер длиной в 20 ступеней (Hyper-Pipelined Technology); Advanced Dynamic Execution; Кэш L1 с отслеживанием исполнения (Trace Cache); Rapid Execution Engine (два устройства ALU, работающие на удвоенной частоте); Advanced Transfer Cache (кэш L2); Streaming SIMD Extensions 2 (SSE2/3).

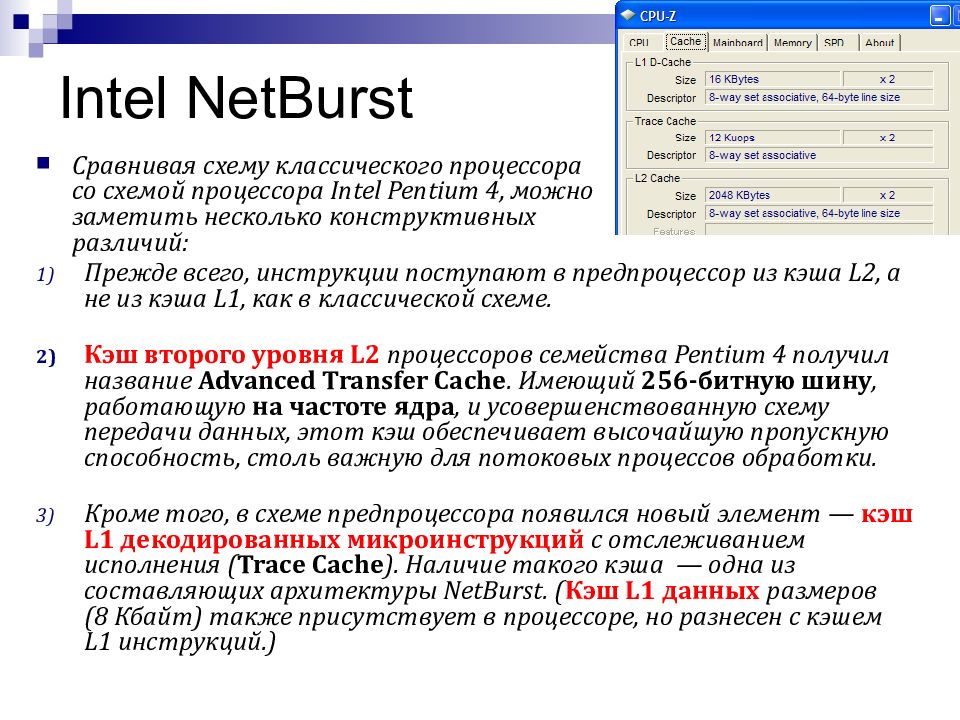

Слайд 106: Intel NetBurst

Сравнивая схему классического процессора со схемой процессора Intel Pentium 4, можно заметить несколько конструктивных различий: Прежде всего, инструкции поступают в предпроцессор из кэша L2, а не из кэша L1, как в классической схеме. Кэш второго уровня L2 процессоров семейства Pentium 4 получил название Advanced Transfer Cache. Имеющий 256-битную шину, работающую на частоте ядра, и усовершенствованную схему передачи данных, этот кэш обеспечивает высочайшую пропускную способность, столь важную для потоковых процессов обработки. Кроме того, в схеме предпроцессора появился новый элемент — кэш L1 декодированных микроинструкций с отслеживанием исполнения ( Trace Cache ). Наличие такого кэша — одна из составляющих архитектуры NetBurst. ( Кэш L1 данных размеров (8 Кбайт) также присутствует в процессоре, но разнесен с кэшем L1 инструкций.)

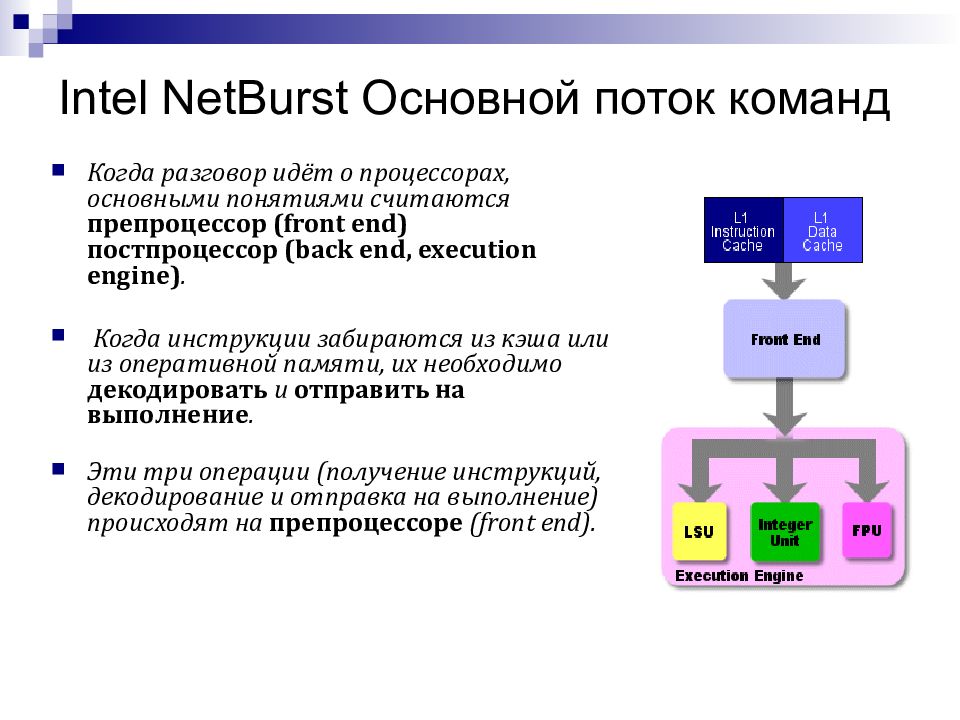

Слайд 107: Intel NetBurst Основной поток команд

Когда разговор идёт о процессорах, основными понятиями считаются препроцессор (front end) постпроцессор (back end, execution engine). Когда инструкции забираются из кэша или из оперативной памяти, их необходимо декодировать и отправить на выполнение. Эти три операции (получение инструкций, декодирование и отправка на выполнение) происходят на препроцессоре (front end).

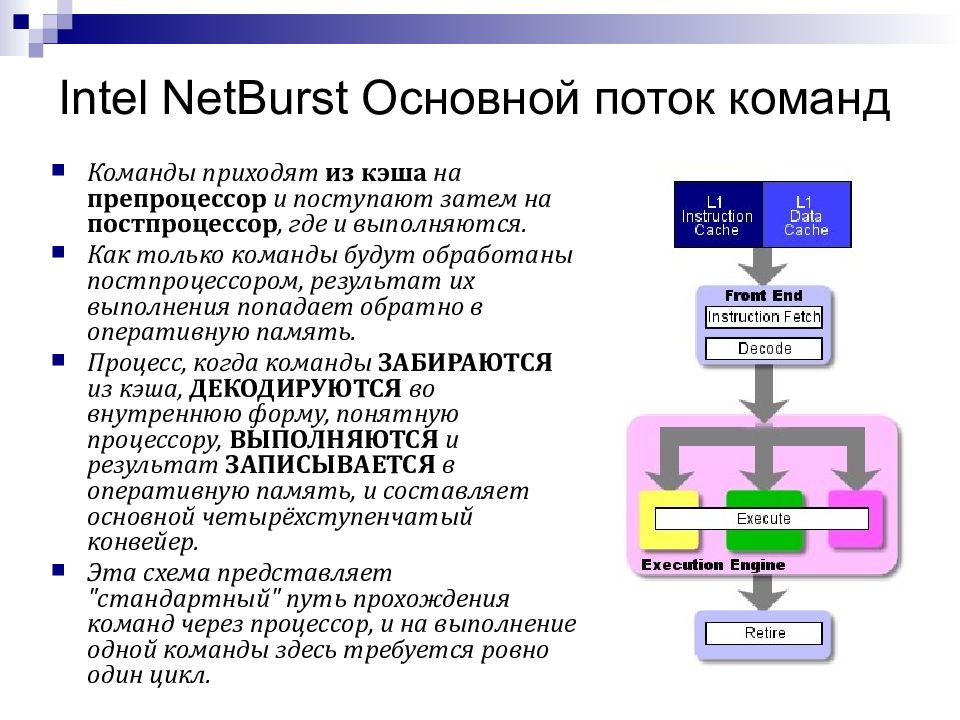

Слайд 108: Intel NetBurst Основной поток команд

Команды приходят из кэша на препроцессор и поступают затем на постпроцессор, где и выполняются. Как только команды будут обработаны постпроцессором, результат их выполнения попадает обратно в оперативную память. Процесс, когда команды ЗАБИРАЮТСЯ из кэша, ДЕКОДИРУЮТСЯ во внутреннюю форму, понятную процессору, ВЫПОЛНЯЮТСЯ и результат ЗАПИСЫВАЕТСЯ в оперативную память, и составляет основной четырёхступенчатый конвейер. Эта схема представляет "стандартный" путь прохождения команд через процессор, и на выполнение одной команды здесь требуется ровно один цикл.

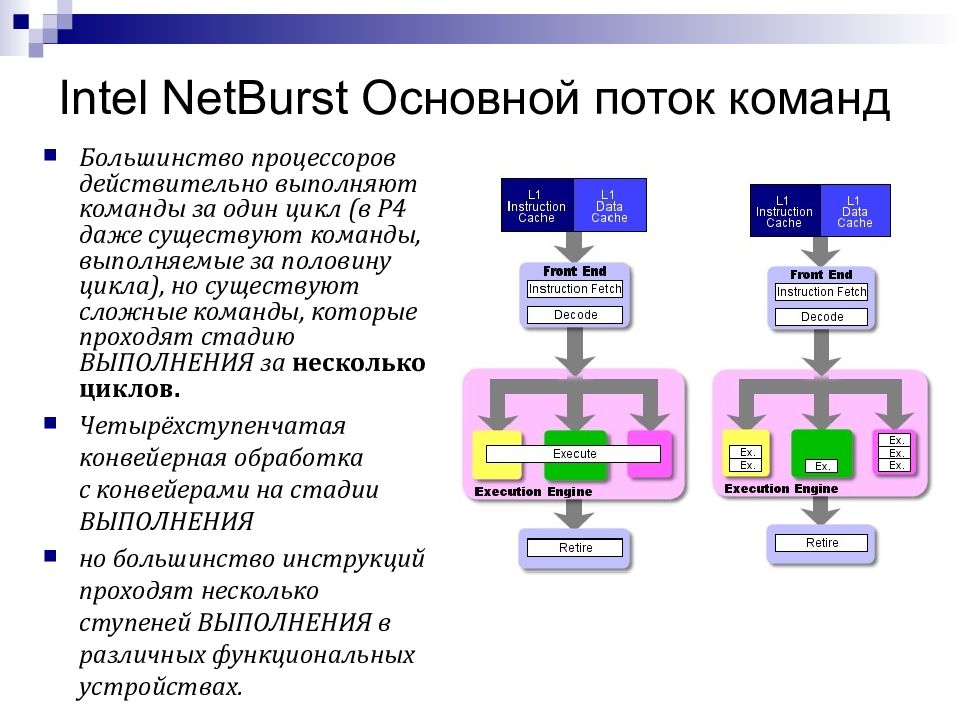

Слайд 109: Intel NetBurst Основной поток команд

Большинство процессоров действительно выполняют команды за один цикл (в P4 даже существуют команды, выполняемые за половину цикла), но существуют сложные команды, которые проходят стадию ВЫПОЛНЕНИЯ за несколько циклов. Четырёхступенчатая конвейерная обработка с конвейерами на стадии ВЫПОЛНЕНИЯ но большинство инструкций проходят несколько ступеней ВЫПОЛНЕНИЯ в различных функциональных устройствах.

Слайд 110: Intel NetBurst Основной поток команд

В отличие от классического варианта, когда весь конвейер состоит из четырёх ступеней (как описано выше), в большинстве современных процессоров всё выглядит несколько по-другому. Например, в G4e вместо классических четырёх ступеней, конвейер разбивается на семь ступеней, что позволяет ему работать на более высокой тактовой частоте при одинаковом технологическом процессе. На каждой из ступеней выполняется меньшее количество работы, но при этом работа выполняется за меньшее количество времени. Так как каждая ступень всегда выполняется ровно за один такт, то более короткие ступени приводят к меньшей продолжительности тактов и возможности работы на более высокой тактовой частоте.

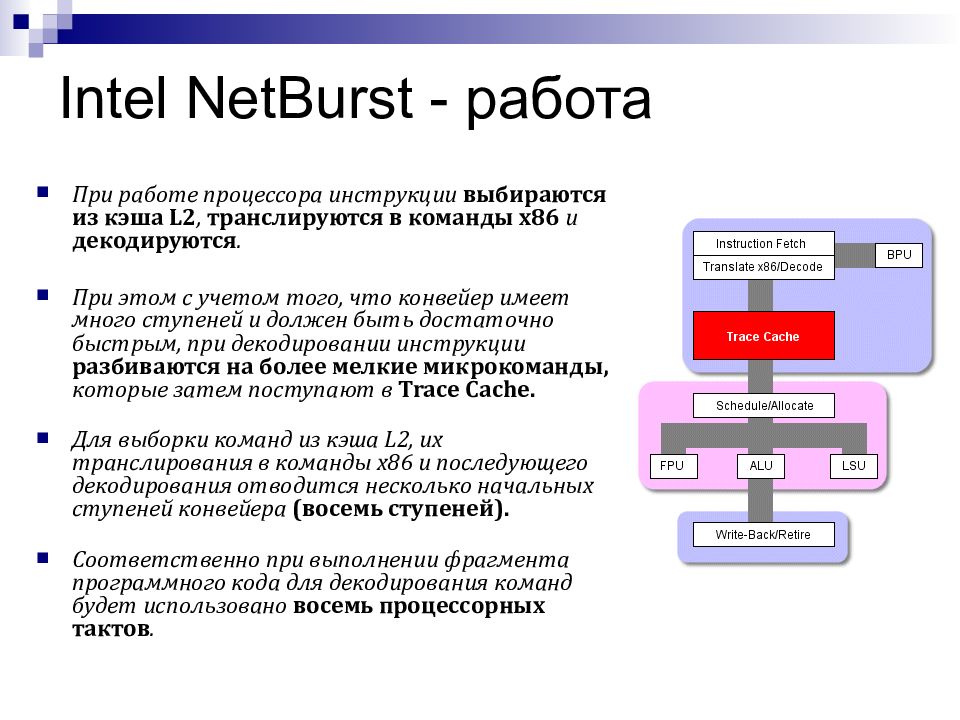

Слайд 111: Intel NetBurst - работа

При работе процессора инструкции выбираются из кэша L2, транслируются в команды х86 и декодируются. При этом с учетом того, что конвейер имеет много ступеней и должен быть достаточно быстрым, при декодировании инструкции разбиваются на более мелкие микрокоманды, которые затем поступают в Trace Cache. Для выборки команд из кэша L2, их транслирования в команды х86 и последующего декодирования отводится несколько начальных ступеней конвейера (восемь ступеней). Соответственно при выполнении фрагмента программного кода для декодирования команд будет использовано восемь процессорных тактов.

Слайд 112: Intel NetBurst – внеочередное выполнение команд

Однако во многих современных (прежде всего мультимедийных) приложениях один и тот же фрагмент кода может повторяться многократно. В этом случае тратить процессорные такты на повторную выборку, транслирование и декодирование было бы нерационально. Выгоднее хранить уже готовые к исполнению микроинструкции в специальном кэше L1, где из них формируются мини-программы, называемые отслеживаниями (traces). При попадании в кэш L1 происходит внеочередное выполнение команд; при этом значительно экономятся ресурсы процессора, так как по своей сути внеочередное выполнение команд подразумевает устранение восьми первых ступеней конвейера, фактическая длина которого в этом случае составляет уже 20 ступеней. В кэше с отслеживанием может храниться до 12 000 декодированных микрокоманд. (При этом заметим, что в процессоре Intel Pentium 4 процент попадания в кэш составляет более 90%.)

Слайд 114: Блок предсказания

Для того чтобы обеспечить высокий процент попаданий в кэш L1 с отслеживаниями (Trace Cache) и построение в нем мини-программ, используется специальный блок предсказания ветвлений (Branch Targets Buffers, BTB и Instruction Translation Look-aside Buffers, I-TLB). Этот блок предсказания позволяет модифицировать мини-программы, основываясь на спекулятивном предсказании. Так, если в программном коде имеется точка ветвления, то блок предсказаний может предположить дальнейший ход программы вдоль одной из возможных ветвей и с учетом этого спекулятивного предсказания построить мини-программу. Кроме того, с кэшем L1 связан также 4-Кбайт буфер ветвлений (BTB). Технология использования кэша с отслеживанием вкупе с усовершенствованным алгоритмом предсказания получила название Advanced Dynamic Execution и является составляющей частью технологии NetBurst.

Слайд 116: Основной конвейер, работа

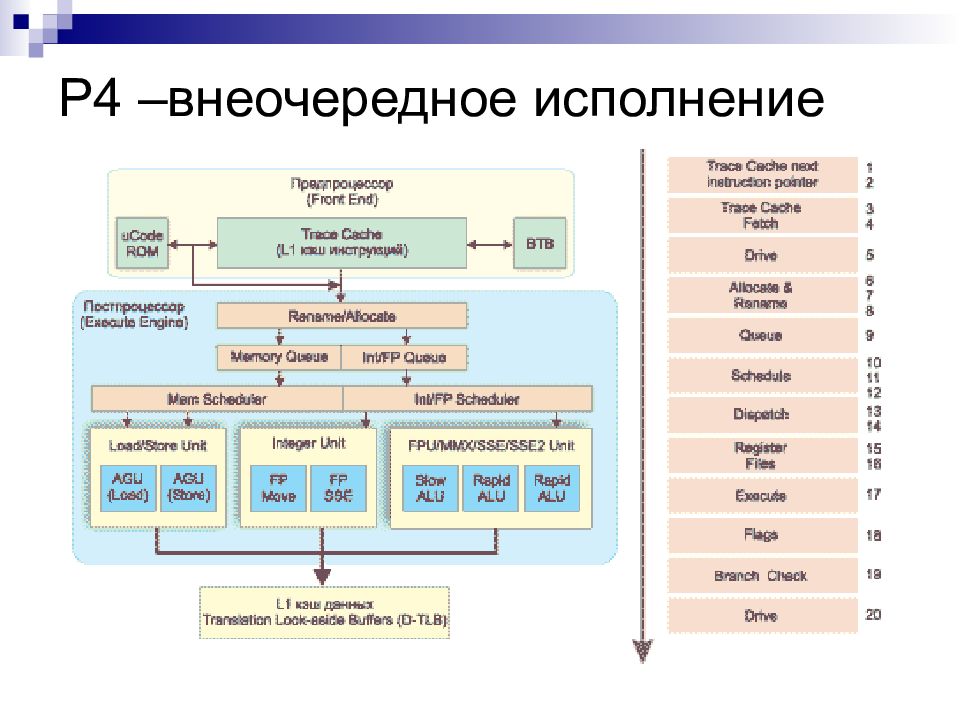

Рассмотрим теперь процесс продвижения микроинструкций по основному конвейеру, то есть когда процессор работает в режиме внеочередного выполнения инструкций. 1-2 такт. В течение первых двух тактов в Trace Cache передается указатель на следующие выполняемые инструкции — это первые две ступени конвейера, называемые Trace Cache next instruction pointer. 3-4 такт. После получения указателя в течение двух тактов происходит выборка инструкций из кэша ( Trace Cache Fetch ) — это две следующие ступени конвейера. После этого выбранные инструкции должны быть отосланы на внеочередное выполнение. Для того чтобы обеспечить продвижение выбранных инструкций по процессору, то есть доставить их из предпроцессора в постпроцессор, используется еще одна дополнительная, или передаточная, ступень конвейера, называемая Drive.

Слайд 117: Основной конвейер, работа

6-7-8 Такт. На следующих трех ступенях (6, 7 и 8) конвейера, называемых Allocate & Rename, происходит переименование и распределение дополнительных регистров процессора. В процессоре Intel Pentium 4 содержится 128 дополнительных регистров, которые не определены архитектурой набора команд. Переименование регистров позволяет добиться их бесконфликтного существования. На 9-й ступени конвейера формируются две очереди микрокоманд: очередь микрокоманд памяти (Mem Queue) и очередь арифметических микрокоманд (Int/FP Queue).

Слайд 118: Основной конвейер, работа

10-11-12 такт. На этих трех ступенях конвейера происходит планирование и распределение (Schedule) микрокоманд. Планировщик выполняет две основные функции: переупорядочивание микрокоманд и распределение их по функциональным устройствам. Суть переупорядочивания микрокоманд заключается в том, что планировщик (Scheduler) определяет, какую из микрокоманд уже можно выполнять, и в соответствии с их готовностью меняет порядок их следования. Распределение микрокоманд происходит по четырем функциональным устройствам, то есть формируются четыре очереди. Первые две из них предназначены для устройств памяти (Load/Store Unit). Эти очереди формируются из очереди памяти Mem Queue. Микрокоманды из очереди арифметических микрокоманд (Int/FP Queue) также распределяются в очереди соответствующих функциональных устройств. Для этого предназначено три распределителя: Fast ALU Scheduler, Slow ALU/General FPU Scheduler Simple FP Scheduler.

Слайд 119: Fast ALU Scheduler

Fast ALU Scheduler — это распределитель простых целочисленных операций. Он собирает простейшие микроинструкции для работы с целыми числами, чтобы затем послать их на исполнительный блок ALU, работающий на двойной скорости. В процессоре Pentium 4 имеется два исполнительных блока ALU, работающих на удвоенной скорости. К примеру, если тактовая частота процессора составляет 2,8 ГГц, то эти два устройства ALU работают с частотой 4,8 ГГц и в параллельном режиме способны выполнять четыре целочисленные операции за один такт. Эти два блока ALU получили название Rapid Execution Engine (блоки быстрого исполнения).

Слайд 120: Распределитель FPU

Slow ALU/General FPU Scheduler — распределитель целочисленных операций/распределитель операций с плавающей точкой. Это устройство распределяет остальные операции ALU и операции с плавающей точкой. Simple FP Scheduler — распределитель простых операций с плавающей точкой. Это устройство формирует очередь простых операций с плавающей точкой и операций по доступу к памяти с плавающей точкой.

Слайд 121: Основной конвейер, работа

13-14 такт. Следующие две ступени конвейера — этап диспетчеризации (Dispatch). На этих ступенях инструкции попадают на один из четырех портов диспетчеризации (dispatch ports), которые выполняют функцию шлюзов к функциональным устройствам. 15-16 такт. После того как инструкции пройдут порты диспетчеризации, они загружаются в блок регистров для дальнейшего выполнения Для этого предназначены следующие две ступени процессора, называемые Register Files. Таким образом, после загрузки инструкций в блок регистров все готово для непосредственного выполнения команд. 17 такт. Процесс непосредственного выполнения инструкций в исполнительных устройствах. Стадия конвейера которая называется Execute.

Последний слайд презентации: Вычислительные системы и телекоммуникации: Основной конвейер, работа

Следующие три ступени конвейера: 18. Ступень изменения состоянии флагов (Flags) — если результат выполнения инструкции этого требует; 19. Ступень проверки ветвления (Branch Check), на которой процессор узнает, сбылось ли предсказание ветвления. 20. Последняя ступень процессора — еще одна передаточная ступень Drive, назначение которой мы уже рассматривали.