Первый слайд презентации: Гарвардская архитектура

Составила: ученица 10 класса,,В ’’ Воробьева Александра

Слайд 2: Гарвардская архитектура

Гарвардская архитектура — архитектура ЭВМ, отличительным признаком которой является раздельное хранение и обработка команд и данных. Говард Эйкен – 1930 г

Слайд 3: Гарвардская архитектура

Гарвардский университет Принстонский университет Советский учёный А. И. Китов фон Неймон

Слайд 4: Классическая гарвардская архитектура

Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий: выборку двух операндов выбор инструкции и её выполнение сохранение результата

Слайд 5: Классическая гарвардская архитектура

В первом компьютере Эйкена «Марк I» для хранения инструкций использовалась перфорированная лента, а для работы с данными — электромеханические регистры. Это позволяло одновременно пересылать и обрабатывать команды и данные, благодаря чему значительно повышалось общее быстродействие

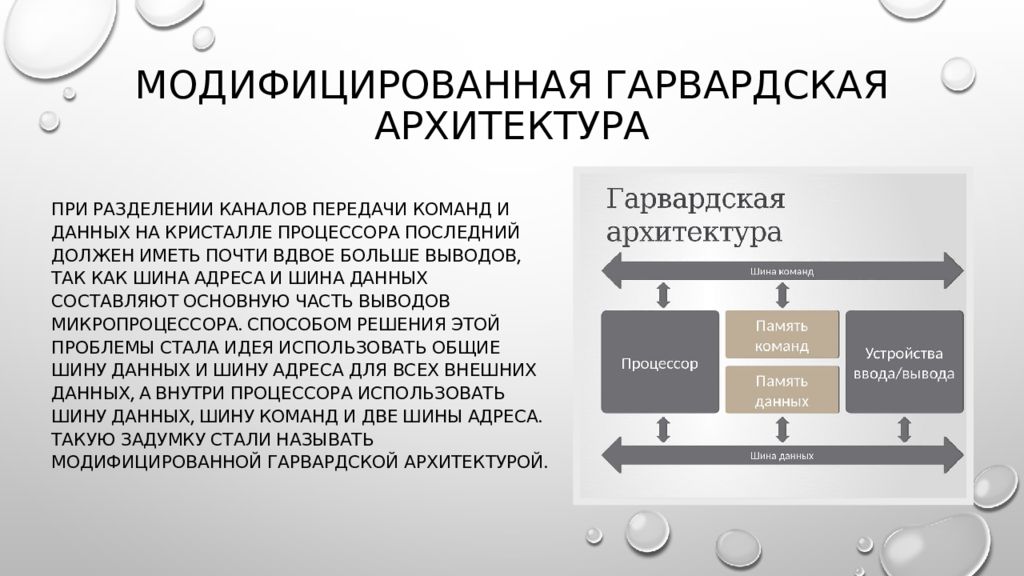

Слайд 6: Модифицированная гарвардская архитектура

При разделении каналов передачи команд и данных на кристалле процессора последний должен иметь почти вдвое больше выводов, так как шина адреса и шина данных составляют основную часть выводов микропроцессора. Способом решения этой проблемы стала идея использовать общие шину данных и шину адреса для всех внешних данных, а внутри процессора использовать шину данных, шину команд и две шины адреса. Такую задумку стали называть модифицированной Гарвардской архитектурой.

Существуют гибридные архитектуры, сочетающие достоинства как Гарвардской, так и фон Неймановской архитектур. процессорное ядро, формально, является гарвардским, но программно оно фон Неймановское, что упрощает написание программ. Современные варианты процессоров могут иногда содержать встроенные контроллеры сразу нескольких разнотипных шин для работы с различными типами памяти — например, Flash. Тем не менее, и в этом случае шины, как правило, используются и для передачи команд, и для передачи данных без разделения, что делает данные процессоры еще более близкими к фон Неймановской архитектуре при сохранении плюсов Гарвардской архитектуры.

Слайд 8: RISC

RISC (компьютер с упрощённым набором команд) — архитектура процессора, в которой быстродействие увеличивается за счёт упрощения команд, чтобы их декодирование было проще, а время выполнения — короче. Первые RISC-процессоры даже не имели команд умножения и деления

Последний слайд презентации: Гарвардская архитектура: Характерные особенности RISC-процессоров

Фиксированная длина машинных команд (например, 32 бита) и простой формат команды. Специализированные команды для операций с памятью — чтения или записи. Операции вида «прочитать-изменить-записать» отсутствуют. Большое количество регистров общего назначения (32 и более). Переименование регистров. Каждый регистр процессора на самом деле представляет собой несколько параллельных регистров, хранящих несколько версий значения.