Первый слайд презентации: Функционалды түйіндер. Шифратор және дешифратор. Мультиплексор және демультиплексор. Компаратор

ЦҚ екі түрге бөлінеді : - комбинациялық сұлбалар ; тізбектелген сұлбалар немесе шектелген автоматтар. Комбинациялық сұлбалар : - дешифратор және шифратор; -мультиплексор және демультиплексор ; - салыстыру сұлбасы немесе компаратор; - жартылай қосындылағыш және сумматор. Автоматтар : Триггер Регистр Санағыш Көпразрядты қосындылағыш

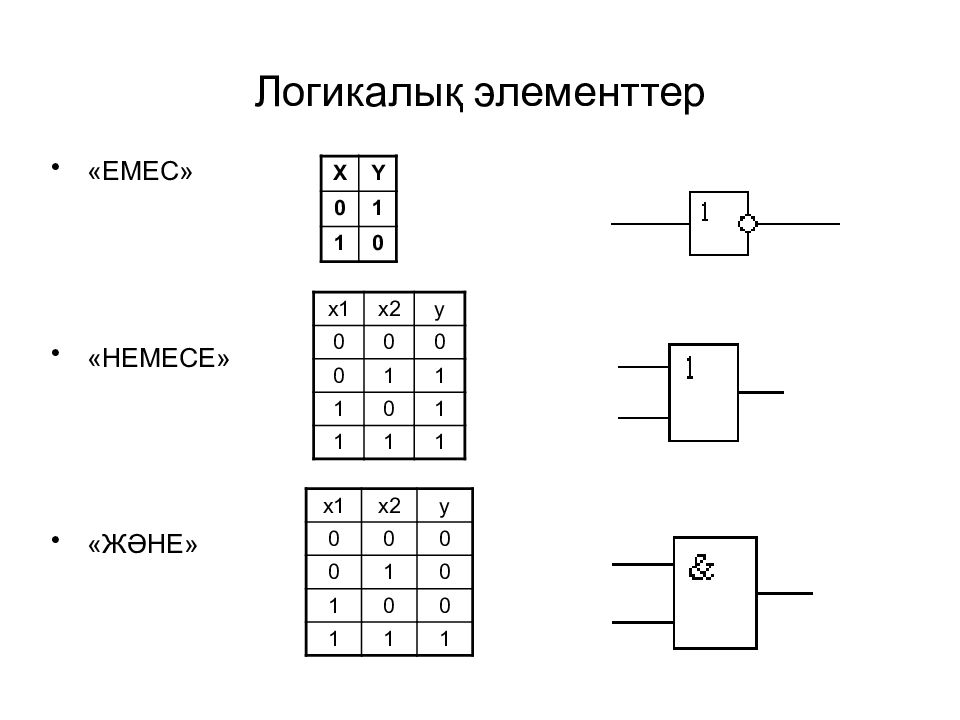

Слайд 2: Логикалық элементтер

«ЕМЕС» «НЕМЕСЕ» «ЖӘНЕ» X Y 0 1 1 0 x1 x2 y 0 0 0 0 1 1 1 0 1 1 1 1 x1 x2 y 0 0 0 0 1 0 1 0 0 1 1 1

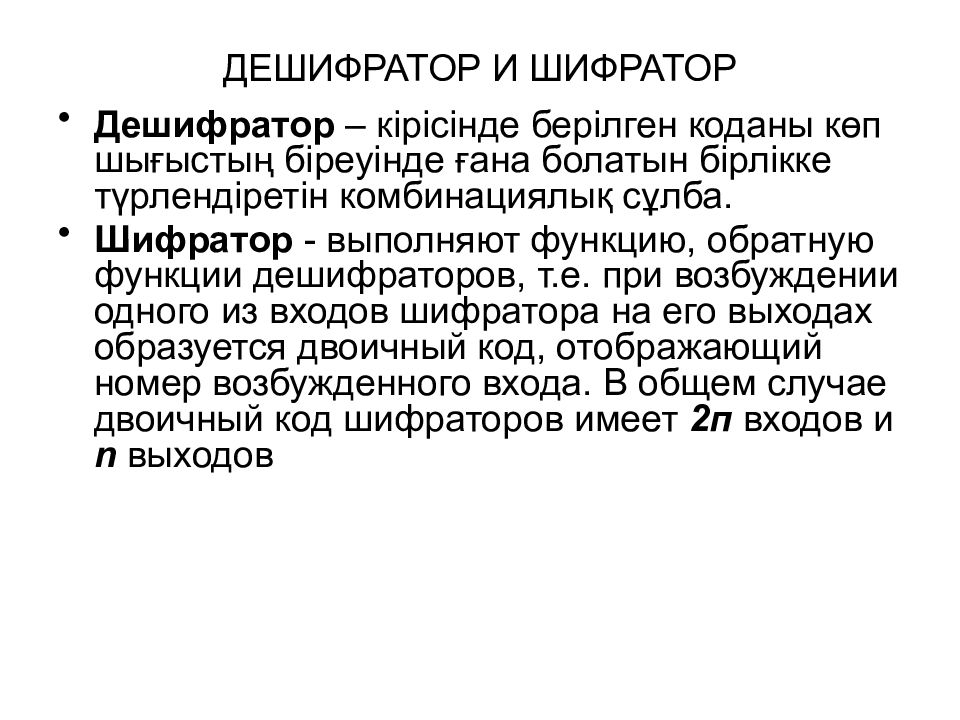

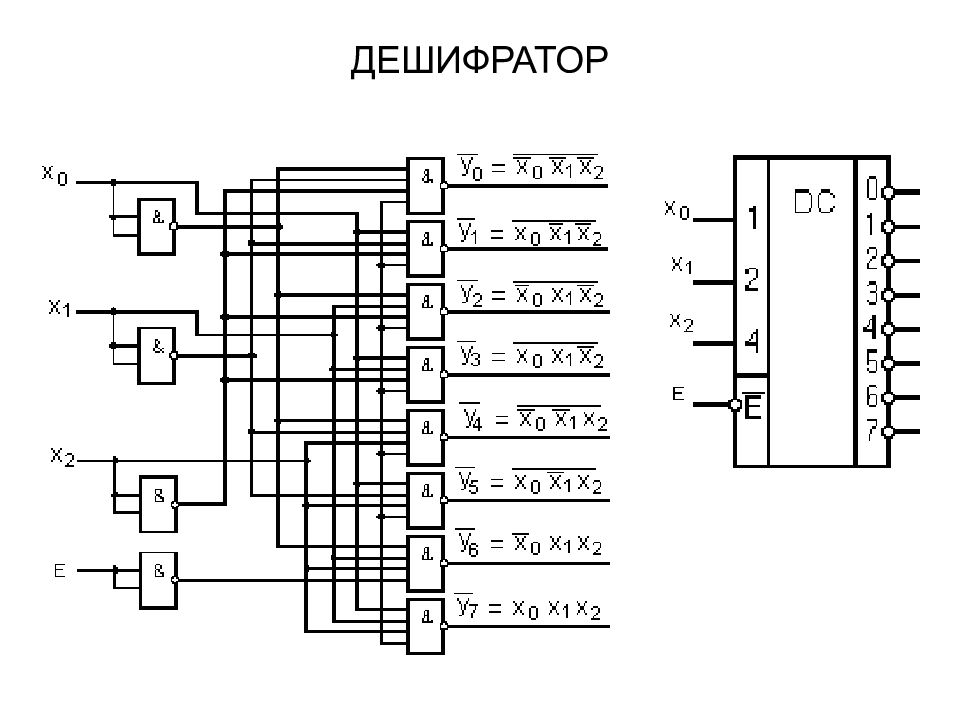

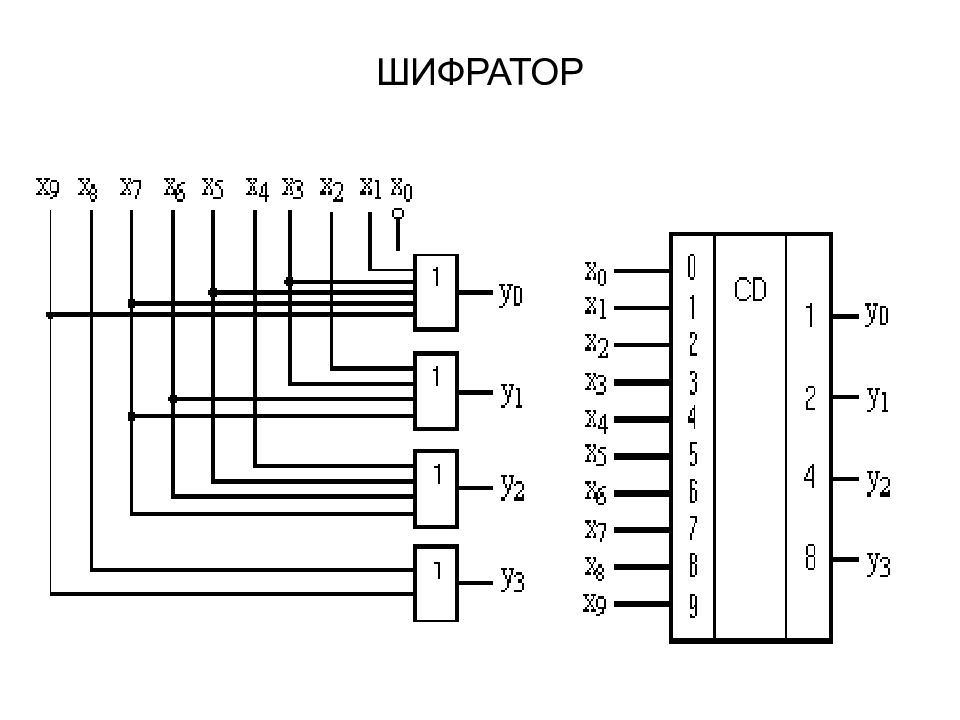

Слайд 3: ДЕШИФРАТОР И ШИФРАТОР

Дешифратор – кірісінде берілген коданы көп шығыстың біреуінде ғана болатын бірлікке түрлендіретін комбинациялық сұлба. Шифратор - выполняют функцию, обратную функции дешифраторов, т.е. при возбуждении одного из входов шифратора на его выходах образуется двоичный код, отображающий номер возбужденного входа. В общем случае двоичный код шифраторов имеет 2п входов и n выходов

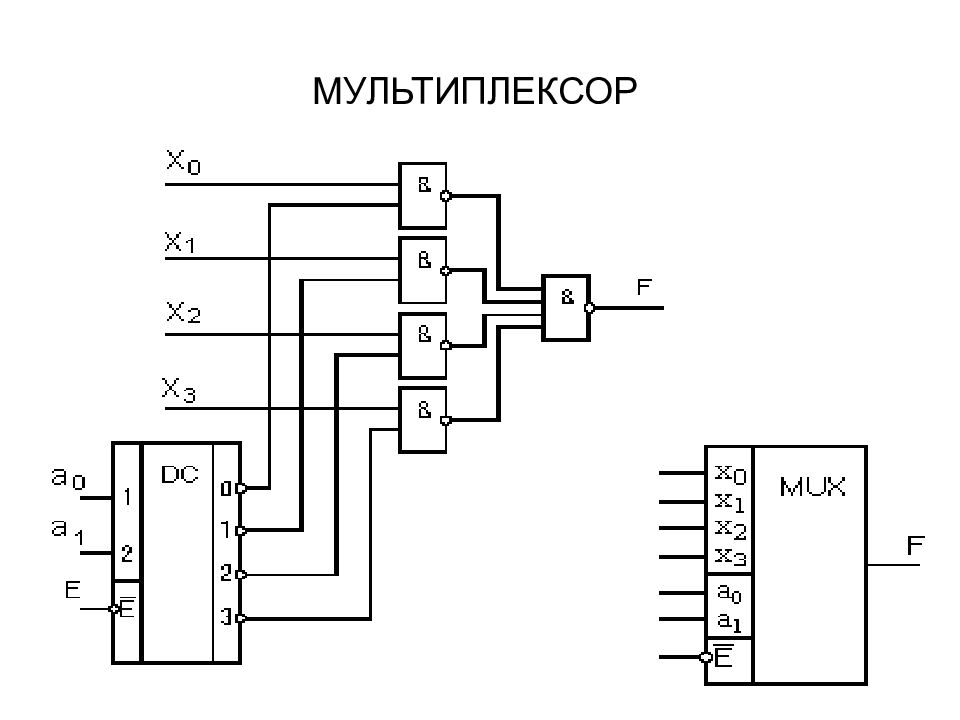

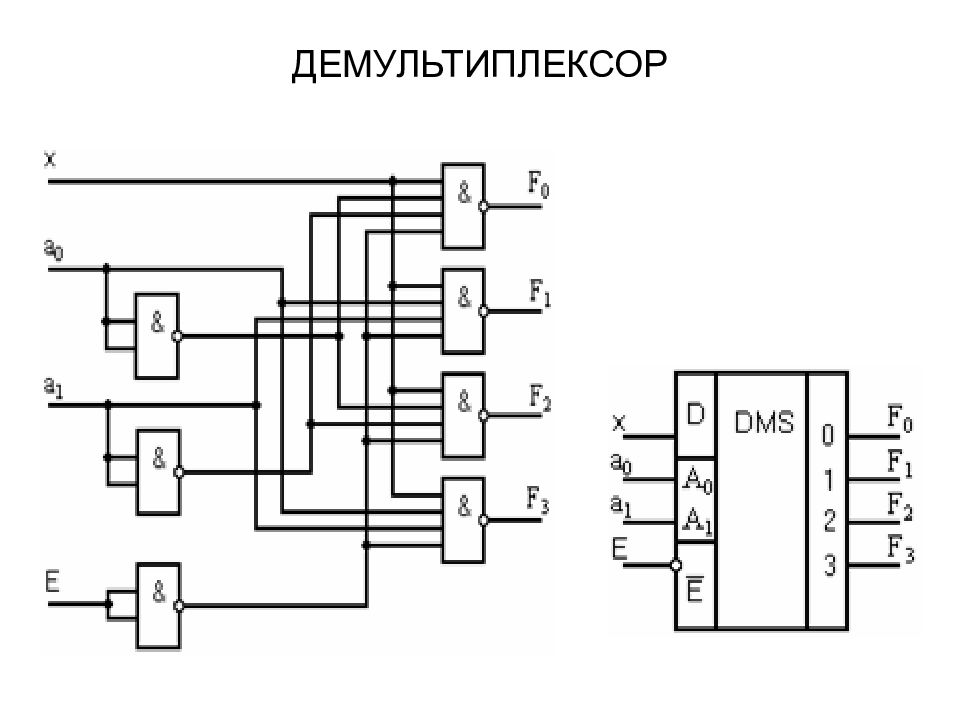

Слайд 6: МУЛЬТИПЛЕКСОР И ДЕМУЛЬТИПЛЕКСОР

Мультиплексором называется комбинационная схема, осуществляющая передачу данных от n входных каналов в один выходной канал. Подключение входных каналов к выходному производится под управлением кода адреса. Демультиплексор имеет один информационный вход и n информационных выходов. Демультиплексоры выполняют функцию, обратную функции мультиплексора.

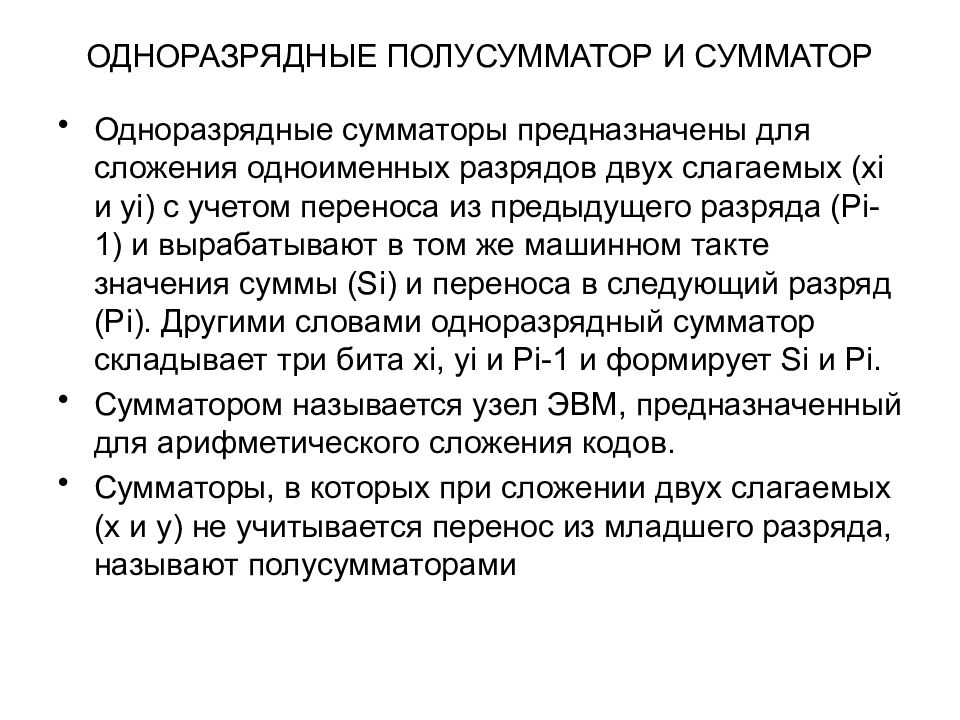

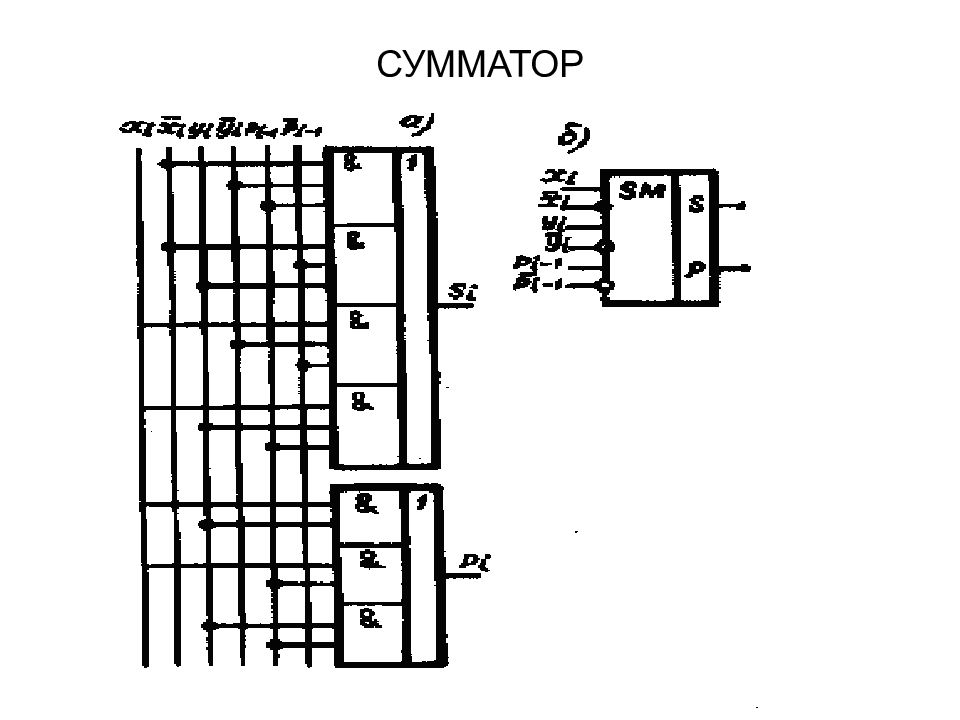

Слайд 10: ОДНОРАЗРЯДНЫЕ ПОЛУСУММАТОР И СУММАТОР

Одноразрядные сумматоры предназначены для сложения одноименных разрядов двух слагаемых (хi и уi) с учетом переноса из предыдущего разряда (Рi-1) и вырабатывают в том же машинном такте значения суммы (Si) и переноса в следующий разряд (Pi). Другими словами одноразрядный сумматор складывает три бита xi, yi и Рi-1 и формирует Si и Рi. Сумматором называется узел ЭВМ, предназначенный для арифметического сложения кодов. Сумматоры, в которых при сложении двух слагаемых (х и у) не учитывается перенос из младшего разряда, называют полусумматорами

Слайд 11: ТАБЛИЦЫ ИСТИННОСТИ ПОЛУСУММАТОРА И СУММАТОРА

xi yi si pi 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 pi -1 xi yi si pi 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1

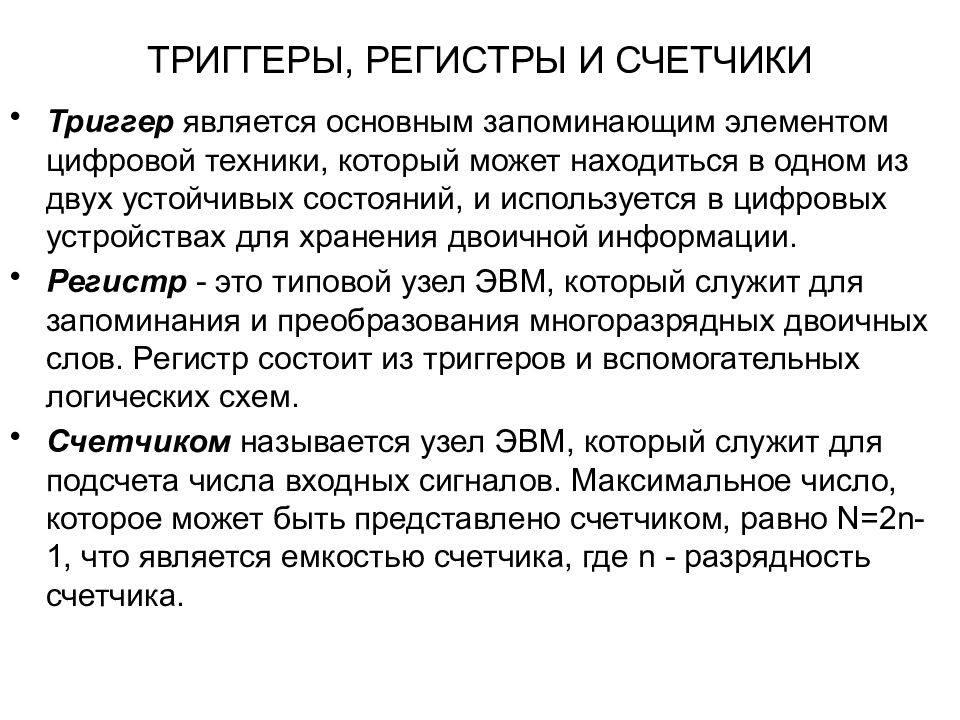

Слайд 14: ТРИГГЕРЫ, РЕГИСТРЫ И СЧЕТЧИКИ

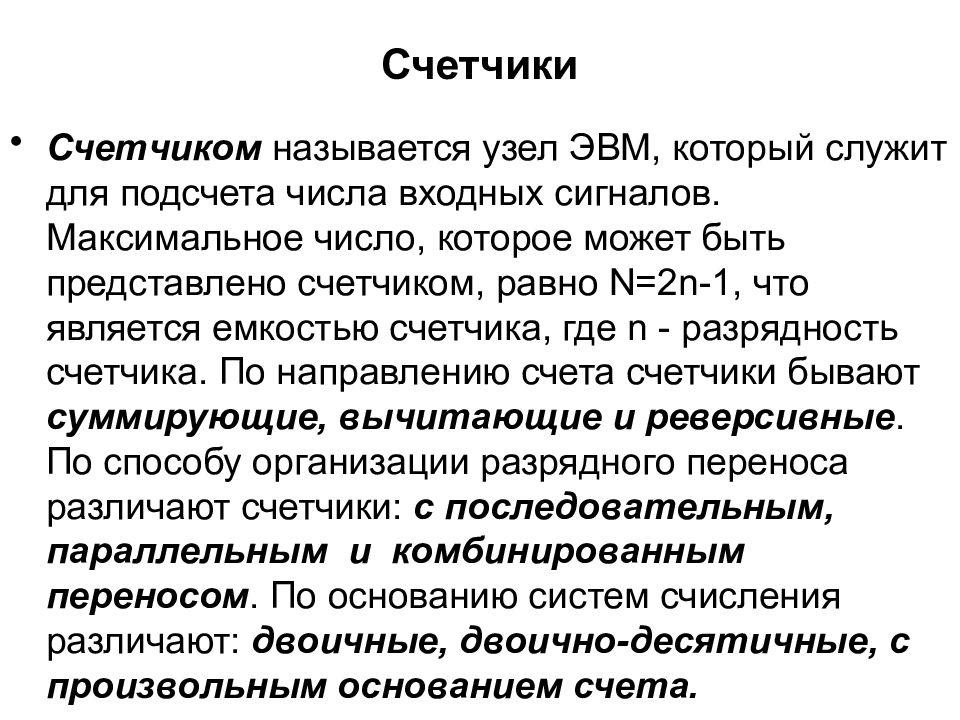

Триггер является основным запоминающим элементом цифровой техники, который может находиться в одном из двух устойчивых состояний, и используется в цифровых устройствах для хранения двоичной информации. Регистр - это типовой узел ЭВМ, который служит для запоминания и преобразования многоразрядных двоичных слов. Регистр состоит из триггеров и вспомогательных логических схем. Счетчиком называется узел ЭВМ, который служит для подсчета числа входных сигналов. Максимальное число, которое может быть представлено счетчиком, равно N=2n-1, что является емкостью счетчика, где n - разрядность счетчика.

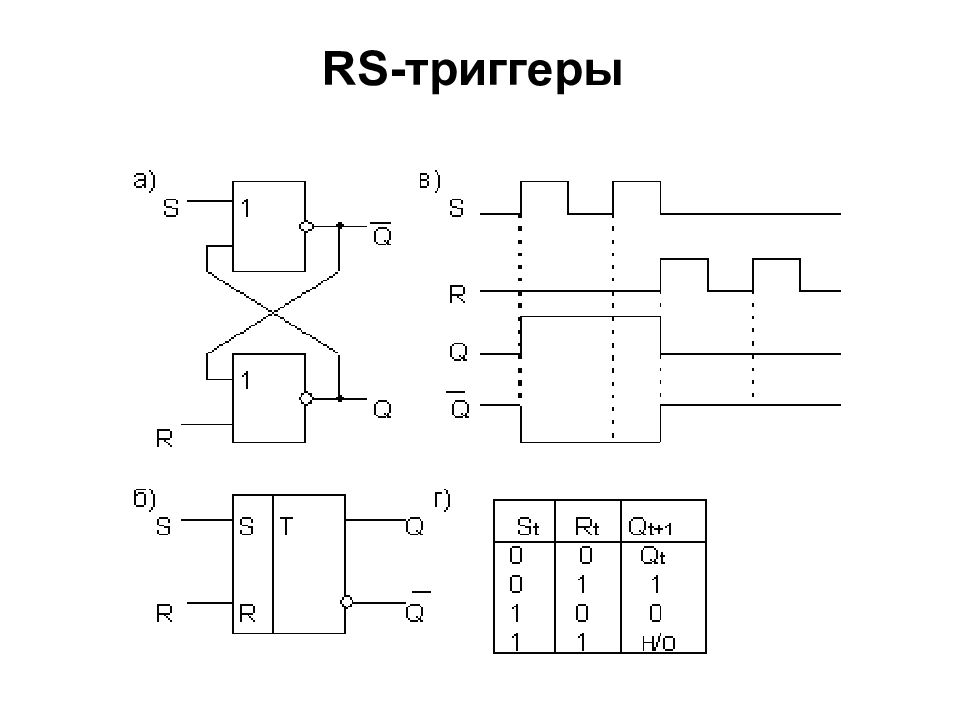

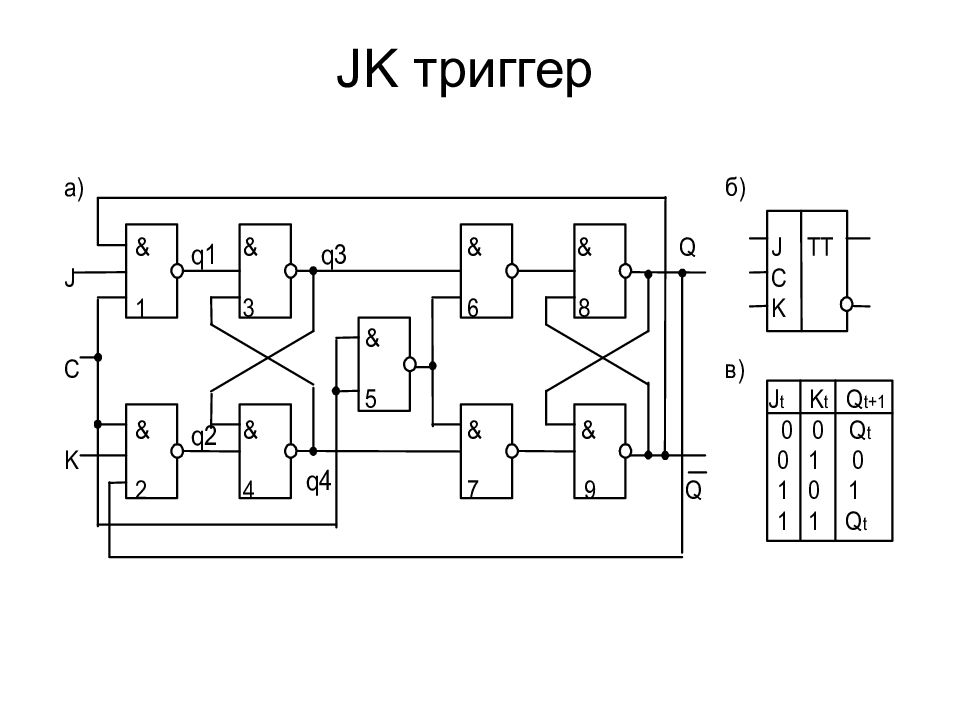

Слайд 15: ТРИГГЕР

Классификация триггеров По методу синхронизации – синхронные и асинхронные: По базису – на основе схем ИЛИ-НЕ, на сонове схем И-НЕ и на комбинационной основе. По типу: - RS ; D ; DV ; T ; TV ; JK. По количеству ступеней бывают триггеры одно- и двухступенчатые.

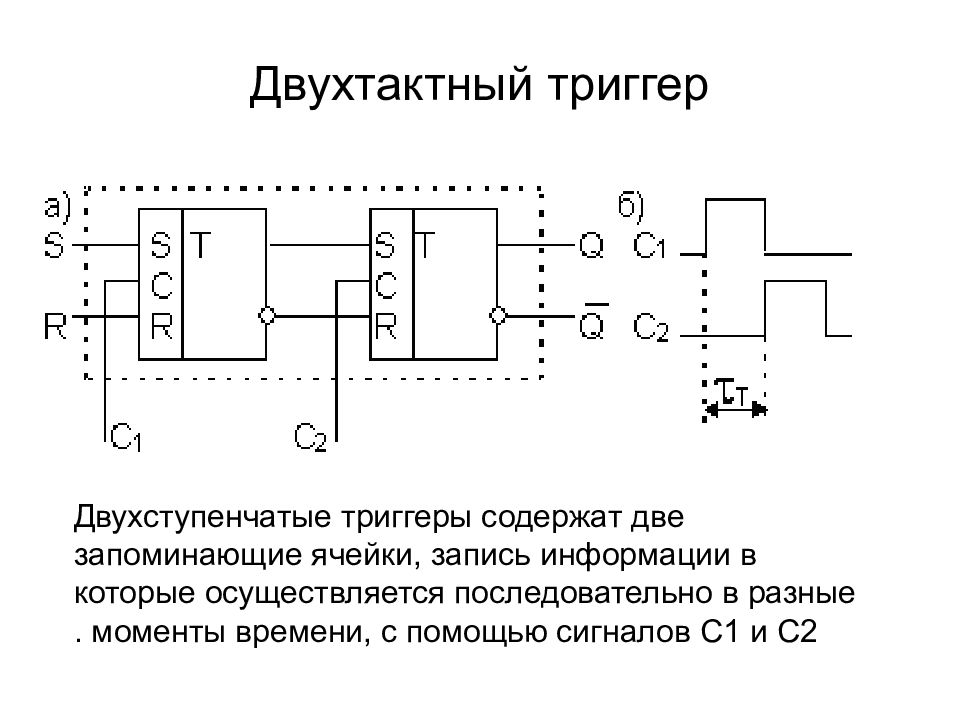

Слайд 17: Двухтактный триггер

Двухступенчатые триггеры содержат две запоминающие ячейки, запись информации в которые осуществляется последовательно в разные. моменты времени, с помощью сигналов С1 и C2

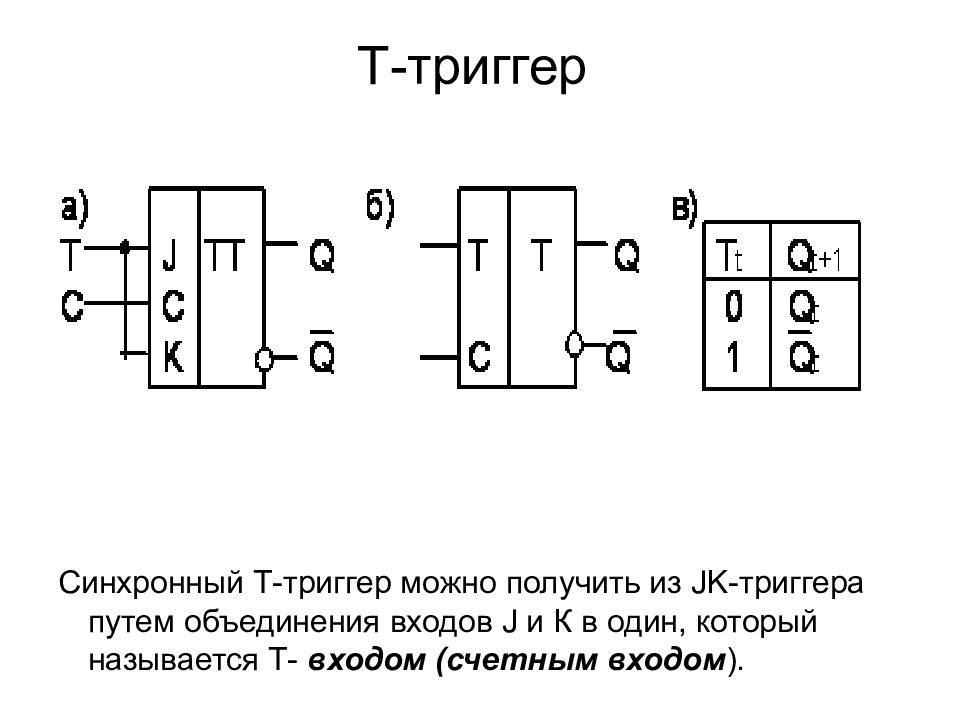

Слайд 19: Т-триггер

Синхронный Т-триггер можно получить из JK-триггера путем объединения входов J и К в один, который называется Т- входом (счетным входом ).

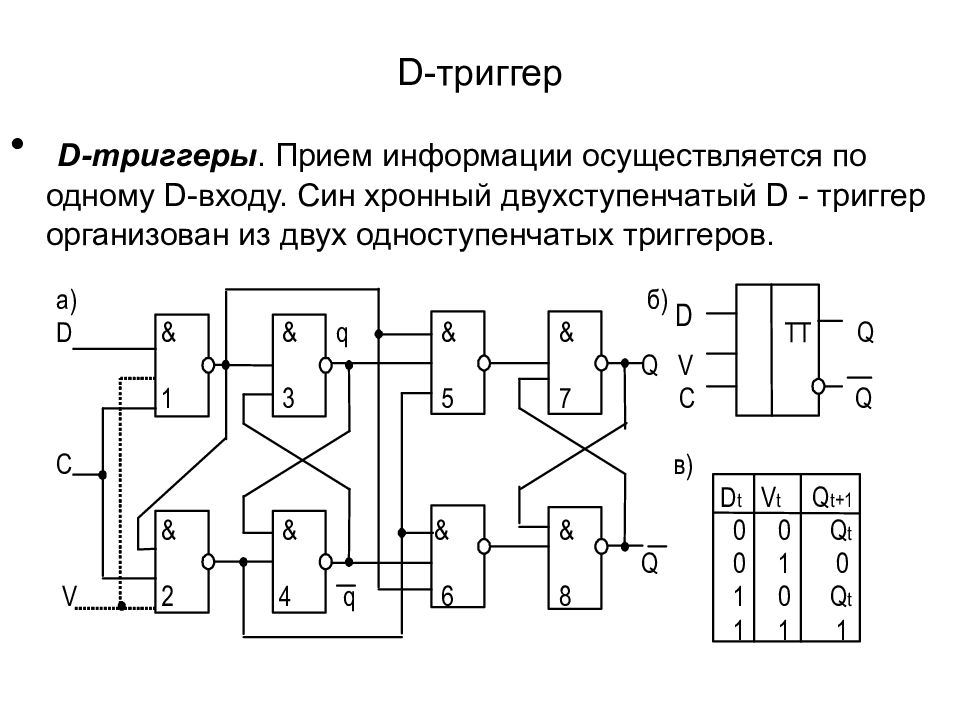

Слайд 20: D- триггер

D-триггеры. Прием информации осуществляется по одному D-входу. Син хронный двухступенчатый D - триггер организован из двух одноступенчатых триггеров.

Слайд 21: Счетчики

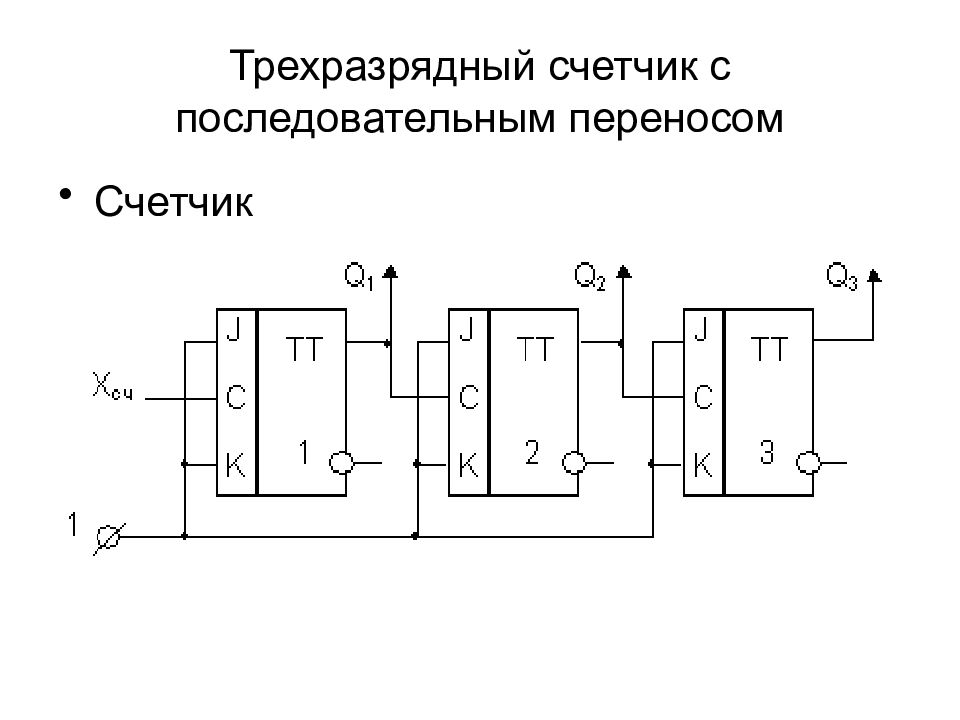

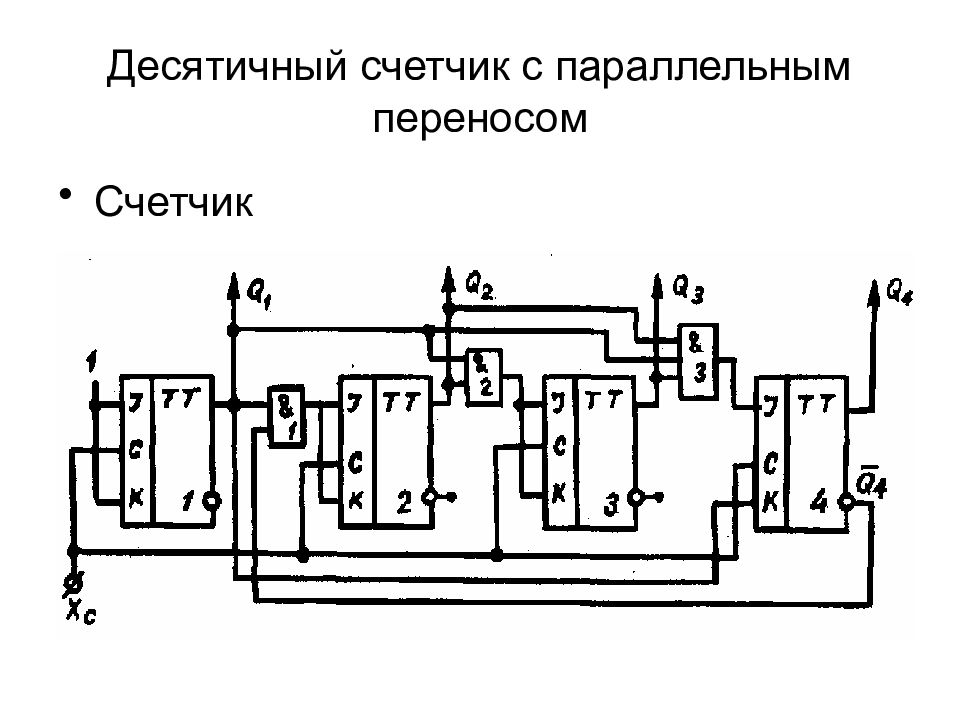

Счетчиком называется узел ЭВМ, который служит для подсчета числа входных сигналов. Максимальное число, которое может быть представлено счетчиком, равно N=2n-1, что является емкостью счетчика, где n - разрядность счетчика. По направлению счета счетчики бывают суммирующие, вычитающие и реверсивные. По способу организации разрядного переноса различают счетчики: с последовательным, параллельным и комбинированным переносом. По основанию систем счисления различают: двоичные, двоично-десятичные, с произвольным основанием счета.

Слайд 24: Многоразрядный сумматор

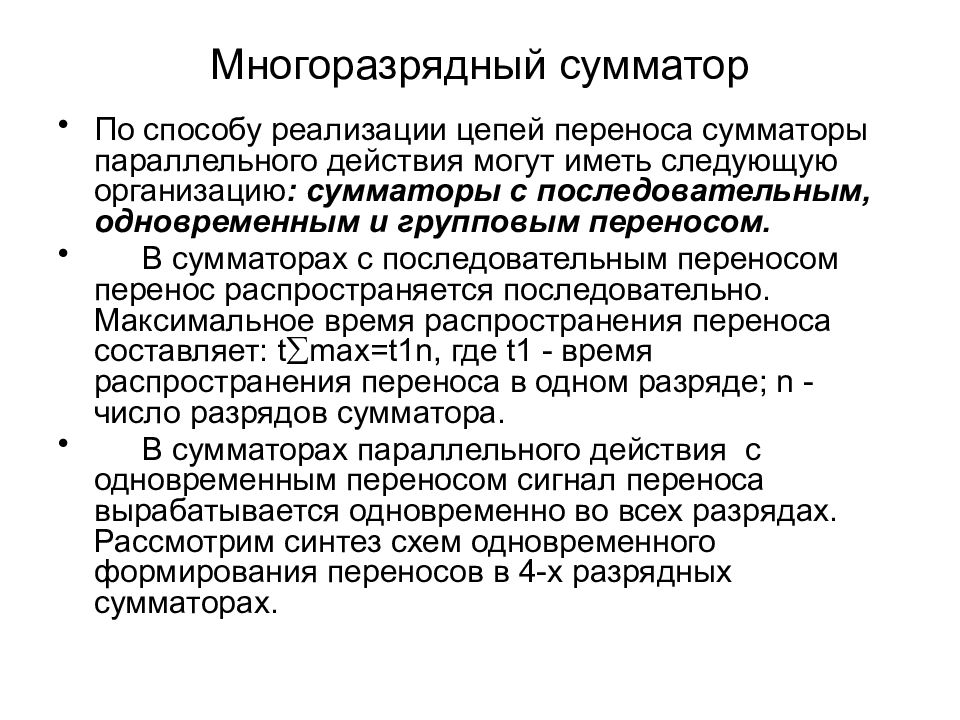

По способу реализации цепей переноса сумматоры параллельного действия могут иметь следующую организацию : сумматоры с последовательным, одновременным и групповым переносом. В сумматорах с последовательным переносом перенос распространяется последовательно. Максимальное время распространения переноса составляет: t max=t1n, где t1 - время распространения переноса в одном разряде; n - число разрядов сумматора. В сумматорах параллельного действия с одновременным переносом сигнал переноса вырабатывается одновременно во всех разрядах. Рассмотрим синтез схем одновременного формирования переносов в 4-х разрядных сумматорах.

Слайд 25: Многоразрядные сумматор

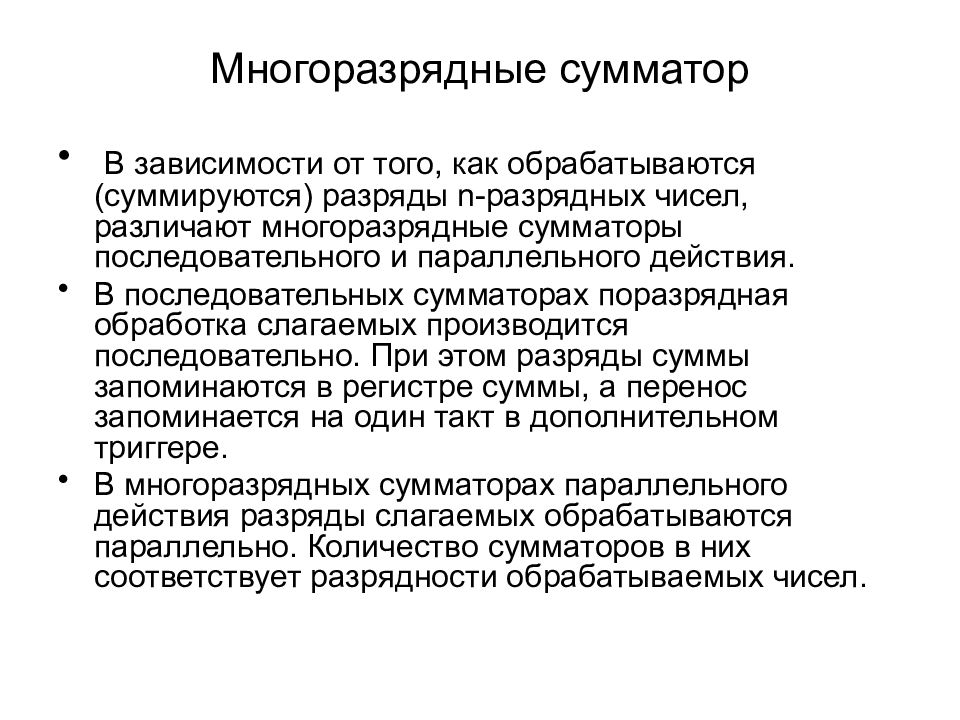

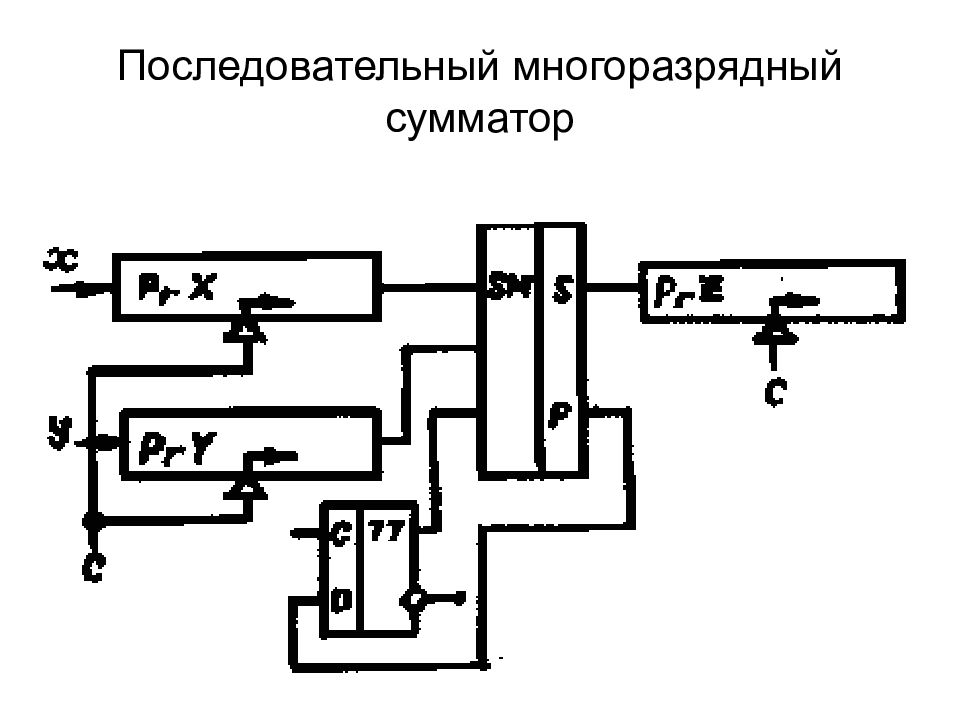

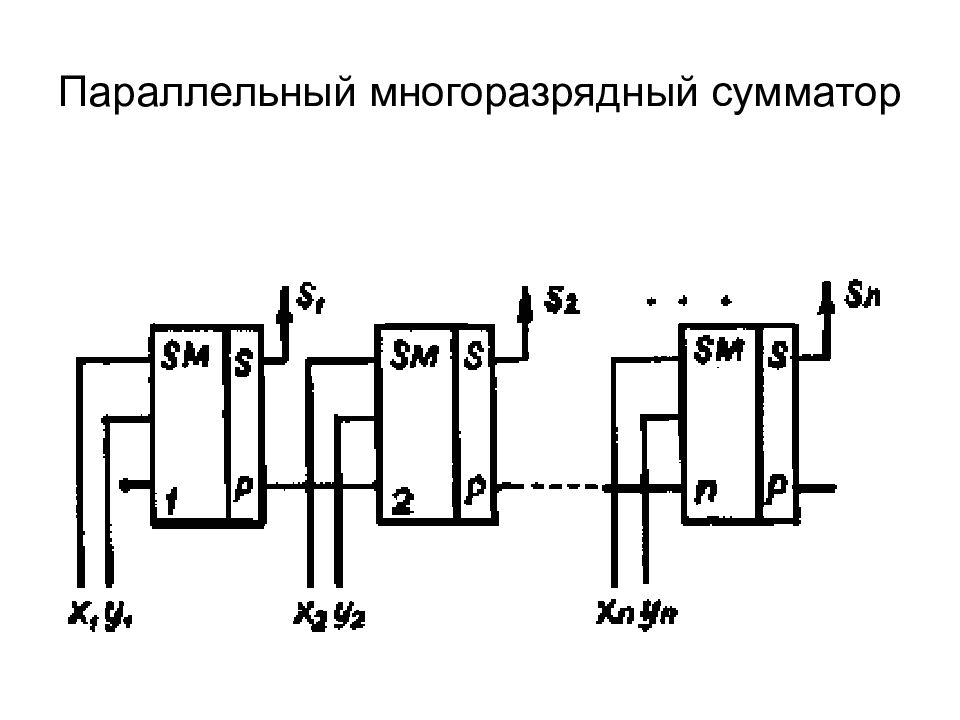

В зависимости от того, как обрабатываются (суммируются) разряды n-разрядных чисел, различают многоразрядные сумматоры последовательного и параллельного действия. В последовательных сумматорах поразрядная обработка слагаемых производится последовательно. При этом разряды суммы запоминаются в регистре суммы, а перенос запоминается на один такт в дополнительном триггере. В многоразрядных сумматорах параллельного действия разряды слагаемых обрабатываются параллельно. Количество сумматоров в них соответствует разрядности обрабатываемых чисел.

Слайд 26: Последовательный многоразрядный сумматор

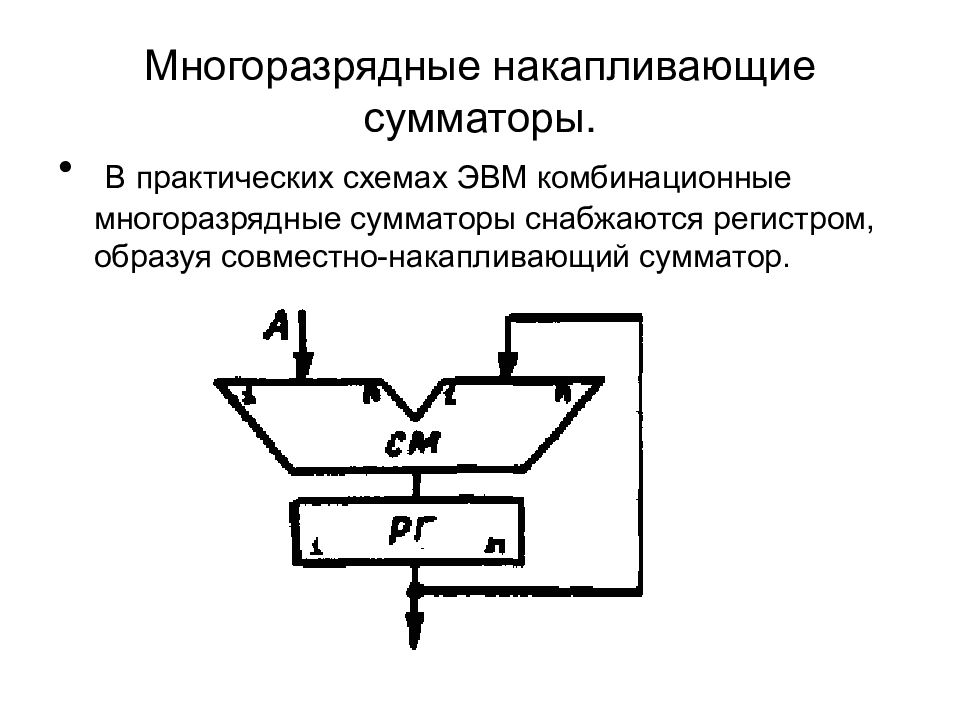

Слайд 28: Многоразрядные накапливающие сумматоры

В практических схемах ЭВМ комбинационные многоразрядные сумматоры снабжаются регистром, образуя совместно-накапливающий сумматор.

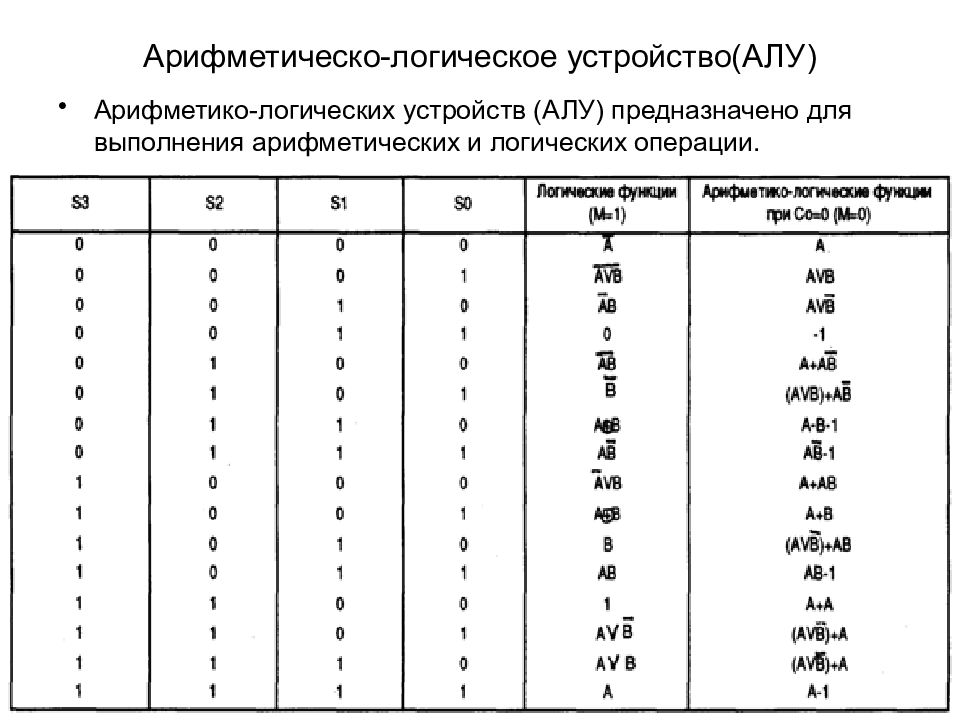

Слайд 29: Арифметическо-логическое устройство(АЛУ)

Арифметико-логических устройств (АЛУ) предназначено для выполнения арифметических и логических операции.